|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## August 2024 Supplementary Examinations

**Programme: B.E.**

**Semester: III**

**Branch: Computer Science and Engineering**

**Duration: 3 hrs.**

**Course Code: 19CS3PCLOD**

**Max Marks: 100**

**Course: Logic Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

|                                                                                                                                                                                                            |   |    | UNIT - I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | CO  | PO        | Marks |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|--|

| 2<br><b>Important Note:</b> Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice. | 1 | a) | Using Quine McClusky method obtain the essential prime implicants for the expression given below:<br>$f(w,x,y,z) = \sum m(1,2,3,5,9,12,14,15) + d_c(4,8,11)$                                                                                                                                                                                                                                                                                                                                  | CO1 | PO1 | <b>10</b> |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            |   | b) | Express the following functions by minterm canonical formula and construct the corresponding truth table<br>$f(X,Y,Z) = X'(Y'+Z) + Z'$                                                                                                                                                                                                                                                                                                                                                        | CO2 | PO2 | <b>05</b> |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            |   | c) | Analyze the following truth table. Express it in the form of SOP. Give the relevant logic diagram                                                                                                                                                                                                                                                                                                                                                                                             | CO2 | PO2 | <b>05</b> |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            |   |    | <table border="1"> <tr><td>X</td><td>Y</td><td>Z</td><td>F</td></tr> <tr><td>0</td><td>0</td><td>0</td><td>1</td></tr> <tr><td>0</td><td>0</td><td>1</td><td>1</td></tr> <tr><td>0</td><td>1</td><td>0</td><td>1</td></tr> <tr><td>0</td><td>1</td><td>1</td><td>0</td></tr> <tr><td>1</td><td>0</td><td>0</td><td>1</td></tr> <tr><td>1</td><td>0</td><td>1</td><td>0</td></tr> <tr><td>1</td><td>1</td><td>0</td><td>1</td></tr> <tr><td>1</td><td>1</td><td>1</td><td>1</td></tr> </table> | X   | Y   | Z         | F     | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |  |  |  |  |

| X                                                                                                                                                                                                          | Y | Z  | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 0                                                                                                                                                                                                          | 0 | 0  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 0                                                                                                                                                                                                          | 0 | 1  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 0                                                                                                                                                                                                          | 1 | 0  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 0                                                                                                                                                                                                          | 1 | 1  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 1                                                                                                                                                                                                          | 0 | 0  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 1                                                                                                                                                                                                          | 0 | 1  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 1                                                                                                                                                                                                          | 1 | 0  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| 1                                                                                                                                                                                                          | 1 | 1  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            |   |    | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |           |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            | 2 | a) | Analyze the following the following scenario: There are 3 inputs x,y,z and 3 outputs a,b,c. When the binary input is 0,1,2,3 the binary output is one greater than the respective input. When binary input is 4,5,6,7 the binary output is one less than the respective binary input. Outline a truth table for this problem and design a simple circuit diagram using separate k maps for each output.                                                                                       | CO2 | PO2 | <b>10</b> |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            |   | b) | Express AND, OR and NAND using NOR gate only.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO3 | PO3 | <b>06</b> |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

|                                                                                                                                                                                                            |   | c) | Write down all the minimal sums of the following Boolean functions using Karnaugh maps<br>$f(a,b,c,d) = \sum m(3,4,6,9,11,12,13,14,15)$                                                                                                                                                                                                                                                                                                                                                       | CO1 | PO1 | <b>04</b> |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |

| <b>UNIT - II</b>  |    |                                                                                                                                                                                                                                                                       |     |     |           |

|-------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 3                 | a) | Design with help of truth table and k-maps 2 bit magnitude comparator                                                                                                                                                                                                 | CO3 | PO3 | <b>08</b> |

|                   | b) | Realize each of the following Boolean expressions using<br>a) an 8-to-1 line multiplexer where w,x, and y appear on select lines S2, S1 and S0 respectively<br>b) an 4 to 1 mux where w and x appear on the select line<br>$f(w,x,y,x)=\sum m(1,2,6,7,9,11,12,14,15)$ | CO1 | PO1 | <b>08</b> |

|                   | c) | Design the following functions using PLA with 3 inputs, 3 product terms, 2 output.<br>$f1(a,b,c)=\sum m(4,5,7)$ $f2(a,b,c)=\sum m(3,5,7)$                                                                                                                             | CO1 | PO1 | <b>04</b> |

| <b>UNIT - III</b> |    |                                                                                                                                                                                                                                                                       |     |     |           |

| 4                 | a) | With a neat diagram outline SISO - Serial IN serial Out register. Also give the timing diagram.                                                                                                                                                                       | CO2 | PO2 | <b>06</b> |

|                   | b) | Derive the excitation table, characteristic equation and state transition diagram of JK and SR Flip flop.                                                                                                                                                             | CO2 | PO2 | <b>10</b> |

|                   | c) | What is bi-stable element. Illustrate how does it succeed in storing 1 bit data using suitable diagram                                                                                                                                                                | CO2 | PO2 | <b>04</b> |

| <b>OR</b>         |    |                                                                                                                                                                                                                                                                       |     |     |           |

| 5                 | a) | Illustrate master slave flip flop. Highlight why M.S flip flop is required.                                                                                                                                                                                           | CO2 | PO2 | <b>08</b> |

|                   | b) | Demonstrate the working of serial-in, parallel-out 4-bit shift register with the help of a neat diagram.                                                                                                                                                              | CO2 | PO2 | <b>06</b> |

|                   | c) | Explain the working of negative edge triggered SR flip flop with the help of a neat diagram. Also, demonstrate the timing diagram for the same.                                                                                                                       | CO2 | PO2 | <b>06</b> |

| <b>UNIT - IV</b>  |    |                                                                                                                                                                                                                                                                       |     |     |           |

| 6                 | a) | Design 3-bit Ripple down counter. Give the timing diagram                                                                                                                                                                                                             | CO3 | PO3 | <b>08</b> |

|                   | b) | Outline the difference between synchronous and asynchronous counter                                                                                                                                                                                                   | CO1 | PO1 | <b>04</b> |

|                   | c) | Design a self-correcting modulo-6 synchronous counter in which all unused state leads to state CBA=000 using JK Flip-flop.                                                                                                                                            | CO3 | PO3 | <b>08</b> |

| <b>UNIT - V</b>   |    |                                                                                                                                                                                                                                                                       |     |     |           |

| 7                 | a) | Design a synchronous logic circuit using Moore model that detects a sequence 101 from an input data stream X and signals detection by making output Z=1, which otherwise is 0. Realize a circuit using JK flip flop.                                                  | CO2 | PO2 | <b>10</b> |

|                   | b) | What is Algorithmic state machine? List any 2 advantages of ASM.                                                                                                                                                                                                      | CO1 | PO1 | <b>02</b> |

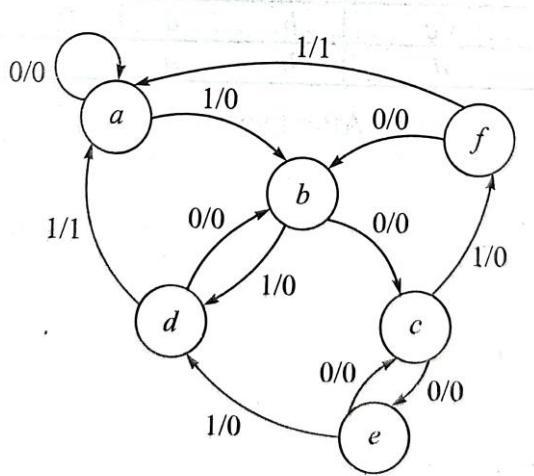

|                   | c) | Apply state reduction technique for the following                                                                                                                                                                                                                     | CO1 | PO1 | <b>08</b> |

CS Scanned with CamScanner

\*\*\*\*\*