|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## April 2024 Semester End Main Examinations

**Programme: B.E.**

**Semester: III**

**Branch: Computer Science and Engineering**

**Duration: 3 hrs.**

**Course Code: 19CS3PCLOD**

**Max Marks: 100**

**Course: Logic Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I  |    |                                                                                                                                                                                                                                  | CO  | PO  | Marks     |

|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 1         | a) | Draw the K-map for the Boolean expression below and simplify to obtain the minimal sum (SOP) and minimal product (POS).<br>$f(w,x,y,z) = \sum(0,1,2,4,5,7,9,12)$<br>Also, draw the logic diagram for the simplified expressions. | CO1 | PO1 | <b>08</b> |

|           | b) | Show the working of AND gate, NOT gate and OR gate using a NOR gate and NAND gate.<br>Also, justify why NOR gate and NAND gate are termed as universal gates.                                                                    | CO1 | PO1 | <b>06</b> |

|           | c) | Analyze the 3-variable K-map given below and check if a hazard exists and draw the equivalent hazard-free circuit as well as the corresponding grouping in the K-map.<br>Also, identify the type of hazard.                      | CO2 | PO2 | <b>06</b> |

| <b>OR</b> |    |                                                                                                                                                                                                                                  |     |     |           |

| 2         | a) | Using Quine McClusky method obtain the essential prime implicants for the expression given below:<br>$f(w,x,y,z) = \sum(1,2,7,9,12,14,15) + dc(0,8,13)$                                                                          | CO1 | PO1 | <b>10</b> |

|           | b) | Simplify the expression given below using K-maps and realize the simplified expression using only NAND gates:<br>$f(a,b,c,d) = \sum m(1,2,3,4,5,13,14) + dc(0,8,9)$                                                              | CO1 | PO1 | <b>10</b> |

| UNIT - II |    |                                                                                                                                                                                                                                  |     |     |           |

| 3         | a) | Realize the given 4-variable expression using 8-to-1 multiplexer as well as 4-to-1 multiplexer.<br>$f(w,x,y,z) = \sum(0,1,3,5,9,11,15)$                                                                                          | CO2 | PO2 | <b>08</b> |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

|   |    |                                                                                                                                                                                                                               |     |     |           |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|   | b) | Design a 3-to-8 decoder to implement the following functions:<br>$f1(x_2, x_1, x_0) = \sum m(0, 2, 6, 7)$<br>$f2(x_2, x_1, x_0) = \sum m(3, 5, 6, 7)$<br>Assume all the 8 output lines of the decoder are active low signals. | CO3 | PO3 | <b>06</b> |

|   | c) | Design a $3 \times 4 \times 2$ PLA for the following functions:<br>$f1(x, y, z) = \sum m(0, 2, 4, 6)$<br>$f2(x, y, z) = \sum m(2, 4, 10)$                                                                                     | CO3 | PO3 | <b>06</b> |

|   |    | <b>UNIT - III</b>                                                                                                                                                                                                             |     |     |           |

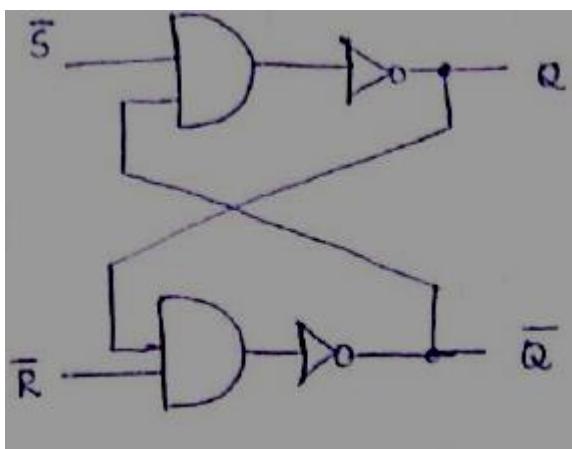

| 4 | a) | Analyze the working of the Flip flop shown below and draw the timing diagram for the same:                                                                                                                                    | CO2 | PO2 | <b>04</b> |

|   |    |                                                                                                                                            |     |     |           |

|   | b) | List different types of Registers. Elaborate on PIPO Register using D Flip Flop.                                                                                                                                              | CO2 | PO2 | <b>06</b> |

|   | c) | Design a JK Flip Flop using SR Flip Flop. Represent the SR Flip Flop as well as JK Flip Flop using state transition diagram. Also, design the excitation table using the constructed state transition diagram.                | CO3 | PO3 | <b>10</b> |

|   |    | <b>OR</b>                                                                                                                                                                                                                     |     |     |           |

| 5 | a) | Explain the working of negative edge triggered SR flip flop with the help of a neat diagram. Also, demonstrate the timing diagram for the same.                                                                               | CO1 | PO1 | <b>06</b> |

|   | b) | Demonstrate the working of serial-in, parallel-out 4-bit shift register with the help of a neat diagram.                                                                                                                      | CO1 | PO1 | <b>06</b> |

|   | c) | Design a serial adder for the addition of two 8-bit numbers using a D flip-flop.                                                                                                                                              | CO3 | PO3 | <b>08</b> |

|   |    | <b>UNIT - IV</b>                                                                                                                                                                                                              |     |     |           |

| 6 | a) | Design a synchronous mod-6 counter using JK flip-flops for the following counting sequence:<br>000, 101, 001, 111, 011, 100, and then back to 000                                                                             | CO3 | PO3 | <b>10</b> |

|   | b) | Design a mod-8 ripple binary asynchronous down counter using JK flip flops.<br>Clearly show the counting sequence, logic circuit as well as the timing diagram.                                                               | CO3 | PO3 | <b>10</b> |

| UNIT - V |    |                                                                                                                                                                                                                  |     |     |           |

|----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 7        | a) | <p>Design a synchronous sequential circuit - Mealy model for the following problem statement:</p> <p>Receive the binary value 101 as input and the output becomes high (1).</p> <p>Also, draw the ASM chart.</p> | CO3 | PO3 | <b>10</b> |

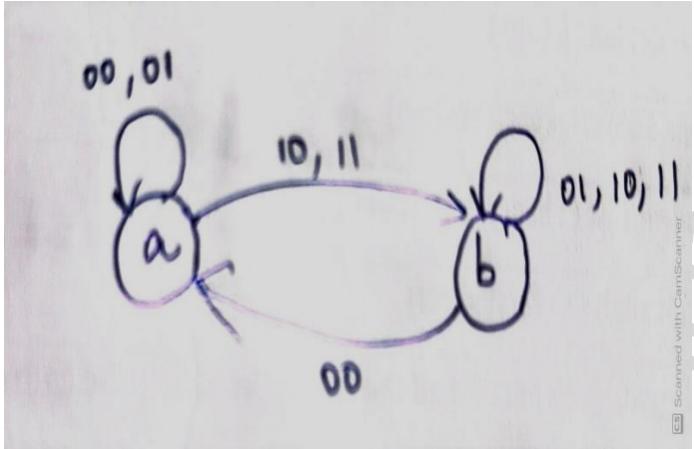

|          | b) | <p>Design an asynchronous sequential logic circuit for the below state transition diagram:</p>                                 | CO3 | PO3 | <b>05</b> |

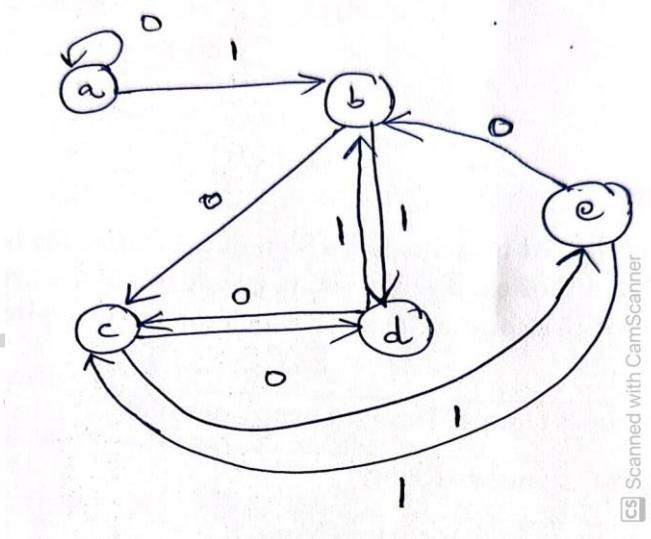

|          | c) | <p>Apply row elimination method to reduce the given state transition diagram:</p>                                            | CO1 | PO1 | <b>05</b> |

\*\*\*\*\*