# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## June / July 2024 Semester End Make-Up Examinations

**Programme: B.E.**

**Branch: Electronics and Communication Engineering**

**Course Code: 23EC3PCAEC**

**Course: Analog Electronic Circuits**

**Semester: III**

**Duration: 3 hrs.**

**Max Marks: 100**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I  |    |                                                                                                                                                                                                                                                                | CO   | PO   | Marks     |

|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------|

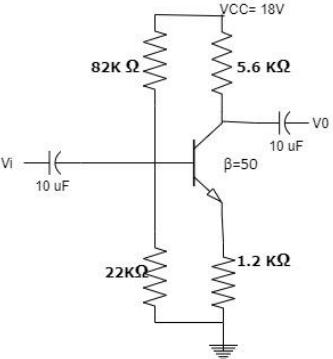

| 1         | a) | <p>Determine the levels of <math>I_{CQ}</math> and <math>V_{CEQ}</math> for the voltage divider bias circuit shown in the figure 1</p>  <p>Figure 1</p>                      | CO 2 | PO 1 | <b>6</b>  |

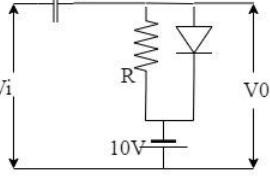

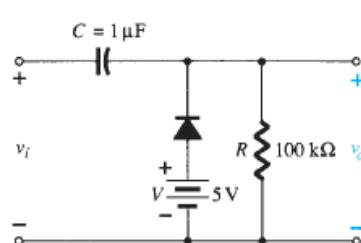

|           | b) | <p>Analyze the circuit shown in Figure 2 and sketch the input and output voltage waveform assuming an ideal diode. (<math>V_i = 20\sin\omega t</math>)</p>  <p>Figure 2</p> | CO3  | PO2  | <b>06</b> |

|           | c) | <p>Draw the <math>r_e</math> model for a voltage divider bias configuration and derive expressions for input impedance, output impedance and voltage gain.</p>                                                                                                 | CO2  | PO1  | <b>08</b> |

| <b>OR</b> |    |                                                                                                                                                                                                                                                                |      |      |           |

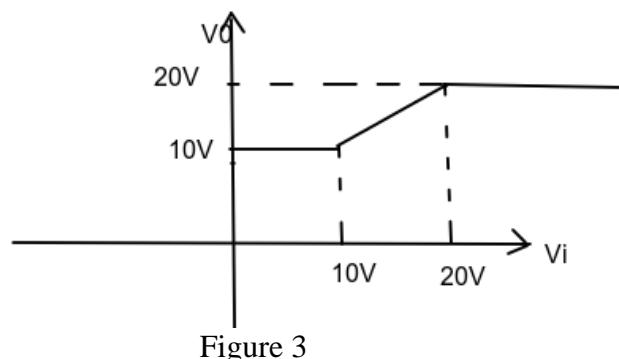

| 2         | a  | <p>For the transfer characteristics shown in figure3 identify and analyze the circuit also obtain the output voltage waveform if the input voltage is <math>50\sin\omega t</math>, (consider ideal diodes)</p>                                                 | CO2  | PO2  | <b>06</b> |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

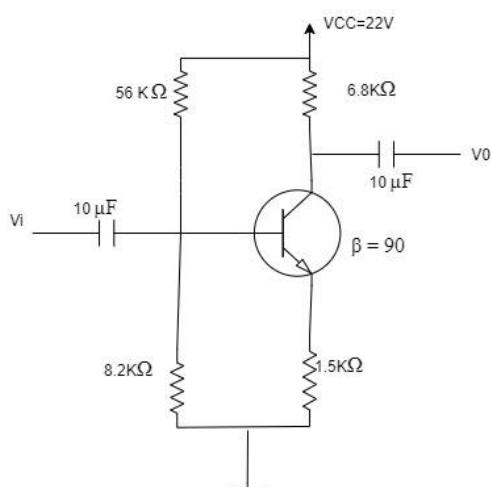

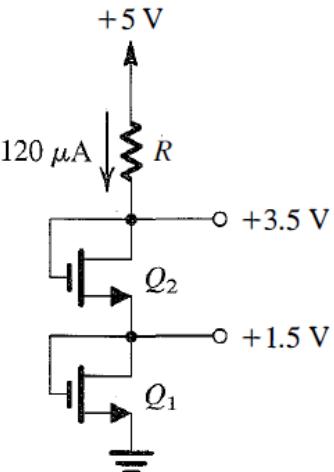

b For the circuit shown in the figure 4. determine the following parameters if  $r_0 = \infty$  and for  $r_0 = 50\text{K}\Omega$

i)  $r_e$  ii)  $Z_i$  iii)  $Z_0$  iv)  $A_v$

Figure 4

c Determine output voltage  $v_o$  for the network of Figure. 5 for the input indicated, sketch the input and output voltage waveform.

Figure 5

## UNIT - II

3 a) With a neat block diagram derive the expressions for gain with feedback, input impedance and output impedance for current series feedback configuration

CO3

PO2

10

b) Calculate gain, input and output admittance for current series feedback amplifier with  $A = -300$ ,  $R_i = 1.5\text{K}\Omega$ ,  $R_o = 50\text{K}\Omega$  and feedback fraction  $\beta = -1/15$

CO2

PO1

04

|   |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |           |

|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|   | c) | Derive an expression for miller effect induced input and output capacitance for an inverting amplifier                                                                                                                                                                                                                                                                                                                                                                                                     | CO2 | PO1 | <b>06</b> |

|   |    | <b>UNIT - III</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |           |

| 4 | a) | A class B power amplifier output stage is required to deliver an average power of 100W into a $16 \Omega$ load. The power supply should be 4V greater than the corresponding peak sine-wave output voltage. Determine the power supply voltage required (to the nearest volt in the appropriate direction), the peak current from each supply, the total supply power, and the power conversion efficiency. Also determine the maximum possible power dissipation in each transistor for a sinewave input. | CO3 | PO2 | <b>10</b> |

|   | b) | With a neat circuit diagram, explain the working of class B push pull power amplifier                                                                                                                                                                                                                                                                                                                                                                                                                      | CO1 | -   | <b>06</b> |

|   | c) | Calculate the total harmonic distortion for an output signal having fundamental amplitude of 2.5V, second harmonic amplitude of 0.25V, third harmonic amplitude of 0.1V and fourth harmonic amplitude of 0.05V.                                                                                                                                                                                                                                                                                            | CO2 | PO1 | <b>04</b> |

|   |    | <b>UNIT - IV</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |     |           |

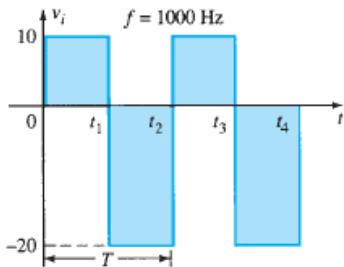

| 5 | a) | The NMOS transistors in the circuit of Fig. 5 have $V_t = 1$ V, $\mu_n C_{ox} = 120 \mu\text{A}/\text{V}^2$ , $\lambda = 0$ , and $L_1 = L_2 = 1 \mu\text{m}$ . Find the required values of gate width for each of $Q_1$ and $Q_2$ , and the value of $R$ , to obtain the voltage and current values indicated.                                                                                                                                                                                            | CO3 | PO2 | <b>10</b> |

|   |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |           |

|   |    | Figure 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |           |

|   | b) | Derive an expression for the drain current of NMOS transistor operating in (i) Triode region and (ii) Saturation region                                                                                                                                                                                                                                                                                                                                                                                    | CO2 | PO1 | <b>10</b> |

|   |    | <b>UNIT - V</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |           |

| 6 | a) | Derive an expression for transconductance of the NMOS transistor and show that the transconductance $gm = \frac{2ID}{2Vov}$                                                                                                                                                                                                                                                                                                                                                                                | CO2 | PO1 | <b>10</b> |

|   | b) | Derive the terminal parameters for the amplifier circuit which does not produce phase reversal at the output                                                                                                                                                                                                                                                                                                                                                                                               | CO3 | PO2 | <b>10</b> |

| <b>OR</b> |    |                                                                                                                                                                |     |     |           |

|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 7         | a) | Derive an expression for i) input impedance ii)output impedance iii)voltage gain and overall voltage gain for a common source amplifier with source resistance | CO2 | PO1 | <b>10</b> |

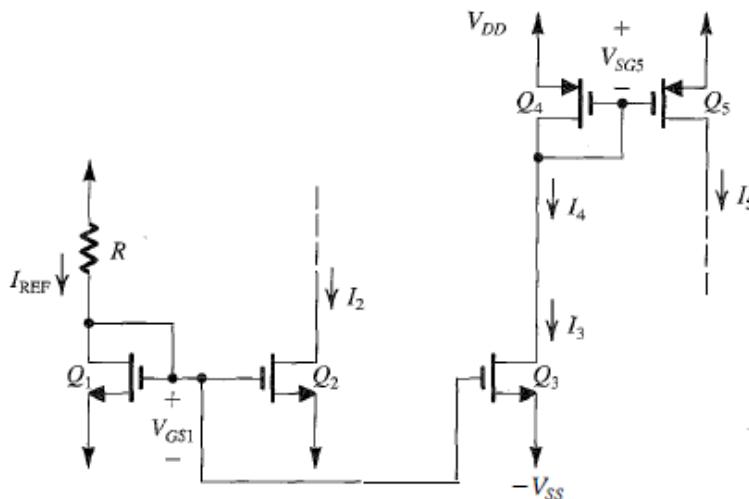

|           | b) | Identify the circuit shown in the figure 9, explain its significance in biasing the MOS amplifier                                                              | CO3 | PO2 | <b>10</b> |

Figure 9

\*\*\*\*\*