# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## April 2024 Semester End Main Examinations

**Programme: B.E.**

**Branch: Electronics and Communication Engineering**

**Course Code: 23EC3PCAEC**

**Course: Analog Electronic Circuits**

**Semester: III**

**Duration: 3 hrs.**

**Max Marks: 100**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I  |    |                                                                                                                                                                                                                                                                                              | CO   | PO  | Marks |

|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|

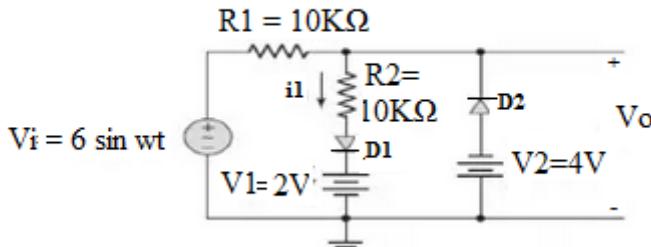

| 1         | a) | <p>Find the output of the parallel based clipper shown in Fig 1a. Assume <math>V_g</math> and <math>r_f=0</math> for the diodes. Illustrate the same with input and output waveforms.</p>  <p>Fig 1a</p> | CO2  | PO1 | 06    |

|           | b) | <p>Determine the operating point (<math>V_{CE}</math>, <math>I_c</math>) for the circuit shown in Fig 1b. Assume <math>\beta</math> of the transistor to be 140.</p>  <p>Fig 1b</p>                      | CO 2 | PO1 | 06    |

|           | c) | <p>For a common emitter amplifier draw <math>r_e</math> model and derive expressions for voltage gain, input impedance, output impedance and current gain.</p>                                                                                                                               | CO 2 | PO1 | 08    |

| <b>OR</b> |    |                                                                                                                                                                                                                                                                                              |      |     |       |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

|   |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |     |           |

|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----------|

| 2 | a) | <p>Determine the current gain, input impedance and voltage gain for a common emitter configuration with a load impedance of <math>2\text{K}\Omega</math>. Assume that the npn transistor used has <math>\beta=120</math> and emitter current of <math>3.2\text{mA}</math>. Let <math>r_0=\infty\Omega</math>.</p>                                                                                                                                                                                                                                                      | CO 2 | PO1 | <b>06</b> |

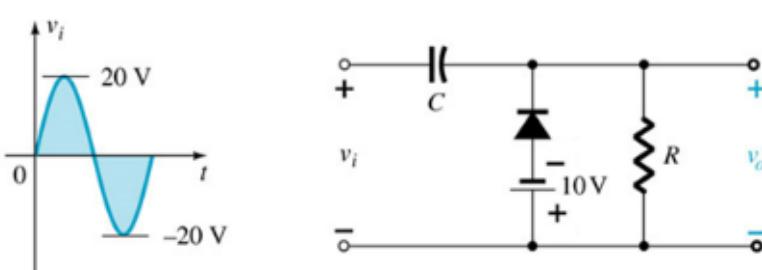

|   | b) | <p>Consider the clamping circuit shown in Fig 2b and plot the output waveform. Assume the diode is ideal.</p>                                                                                                                                                                                                                                                                                                                                                                        | CO 2 | PO1 | <b>06</b> |

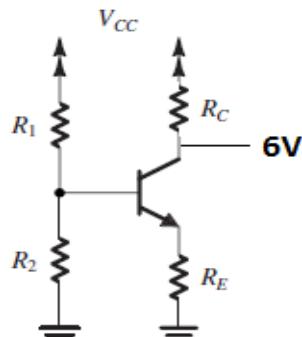

|   | c) | <p>Design the bias network of the amplifier shown in Fig. 2c to establish a current <math>I_E = 1 \text{ mA}</math> using a power supply <math>V_{CC} = +12 \text{ V}</math>. The transistor is specified to have a nominal <math>\beta = 100</math>. Allocate one-third of the supply voltage to the voltage drop across <math>R_2</math> and <math>I_E=1\text{mA}</math>.</p>                                                                                                     | CO 4 | PO3 | <b>08</b> |

|   |    | <b>UNIT - II</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |           |

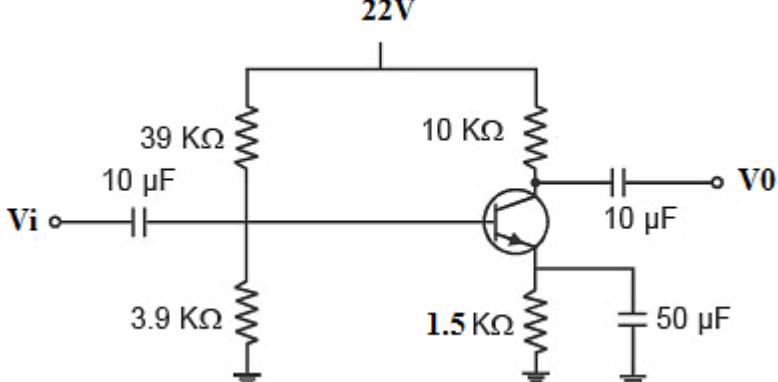

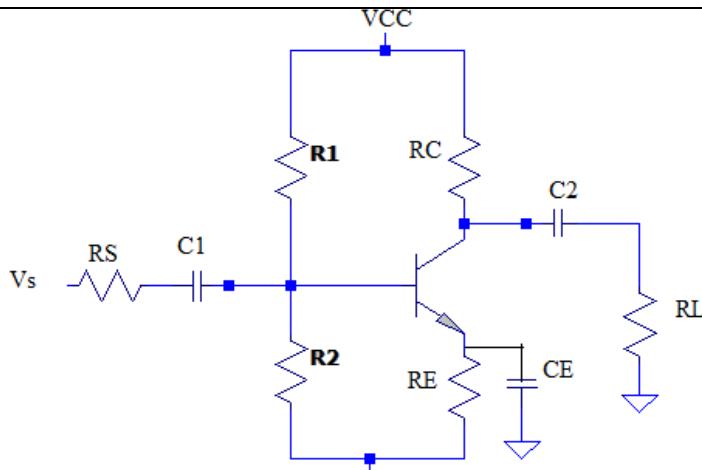

| 3 | a) | <p>Determine the Voltage gain <math>V_0/V_i</math>, <math>V_0/V_s</math> and lower cutoff frequency for the circuit shown in Fig 3a. Assume <math>C_1= 10\mu\text{F}</math>, <math>C_E= 20 \mu\text{F}</math>, <math>C_2= 1 \mu\text{F}</math>, <math>R_s= 1\text{K}\Omega</math>, <math>R_1= 40 \text{ K}\Omega</math>, <math>R_2=10 \text{ K}\Omega</math>, <math>R_E=2 \text{ K}\Omega</math>, <math>R_C=4 \text{ K}\Omega</math>, <math>R_L=2.2 \text{ K}\Omega</math>, <math>\beta=100</math>, <math>V_{cc}=20\text{V}</math>, <math>r_0=\infty\Omega</math>.</p> | CO 2 | PO1 | <b>10</b> |

Fig 3a

b) An amplifier has a gain  $A$ , input impedance  $R_i$  and output impedance  $R_o$ . Derive the expression for input and output impedance when a voltage series negative feedback is provided to the amplifier with a feedback factor  $\beta$ .

### UNIT - III

4 a) For a series fed class A power amplifier prove that maximum efficiency is 25%.

b) For a class B amplifier using a supply of  $V_{cc}=30V$  and driving a load of  $16\Omega$ , find the maximum input power, output power and transistor dissipation.

c) Analyse the working of a transformer coupled class B power amplifier and also the drawbacks of the same.

### UNIT - IV

5 a) With suitable figures deduce  $I_d$ -  $V_{ds}$  relationship in linear and in saturation region

b) With neat sketches explain the device structure and operation of NMOSFET for various conditions of  $V_{gs}$  and  $V_{ds}$ .

### UNIT - V

6 a) Analyse the working of a common source amplifier with degeneration resistance and arrive at the expressions for voltage gain and output impedance of the amplifier.

b) Derive an expression for output impedance of Wilson mirror using MOSFETS

### OR

7 a) Analyse a Common Gate amplifier with resistive load. Obtain the expression for small signal voltage gain. Draw the small signal equivalent circuit and obtain the expressions.

b) Deduce relevant expression for voltage gain of a source follower with a small signal model.

\*\*\*\*\*