# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## June 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: III**

**Branch: Electronics and Communication Engineering**

**Duration: 3 hrs.**

**Course Code: 23EC3PCAEC**

**Max Marks: 100**

**Course: Analog Electronic Circuits**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>                                                                                                                                                                                |    |                                                                                                                                                                                        | <b>CO</b>   | <b>PO</b>   | <b>Marks</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|

| Important Note: Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice. | 1  | a) What are clampers? Explain the working of a positive clamp with relevant diagrams and waveforms.                                                                                    | <i>CO1</i>  | -           | <b>05</b>    |

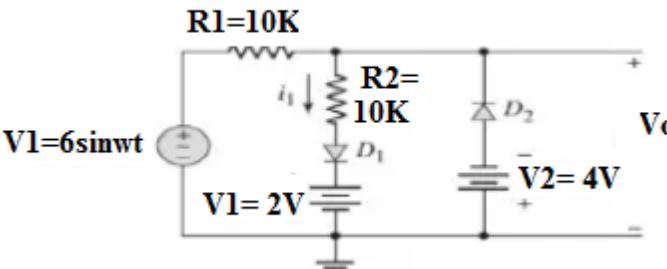

|                                                                                                                                                                                                | b) | Sketch the output wave form for the circuit shown in Fig 1b.                                                                                                                           | <i>CO 2</i> | <i>PO1</i>  | <b>05</b>    |

|                                                                                                                                                                                                |    |  <p style="text-align: center;">Fig 1b</p>                                                         |             |             |              |

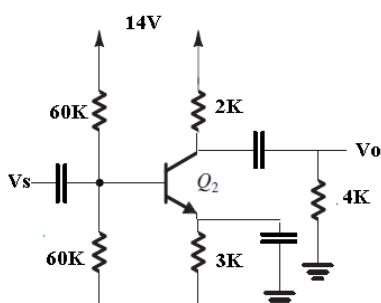

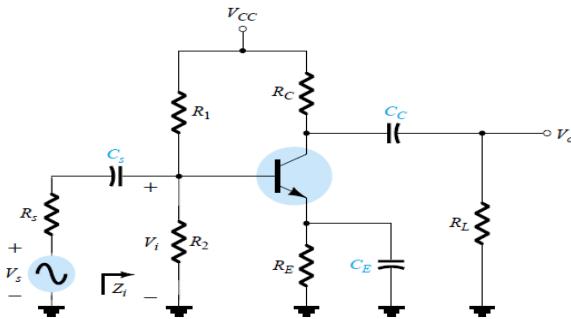

|                                                                                                                                                                                                | c) | Find the operating point of the Si NPN transistor, the small signal voltage gain, $R_{in}$ and $R_{out}$ for the amplifier circuit shown in Fig 1c. Let $r_0=\infty$ and $\beta=199$ . | <i>CO 2</i> | <i>PO 1</i> | <b>10</b>    |

|                                                                                                                                                                                                |    |  <p style="text-align: center;">Fig 1c</p>                                                          |             |             |              |

|                                                                                                                                                                                                |    | <b>OR</b>                                                                                                                                                                              |             |             |              |

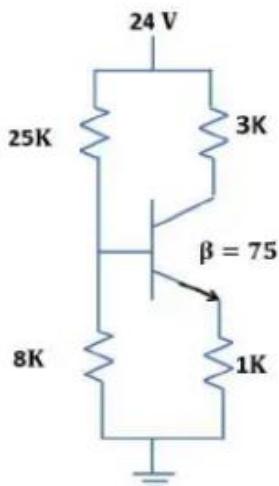

| 2                                                                                                                                                                                              | a) | Find the operating point for the circuit shown in Fig 2a                                                                                                                               | <i>CO 2</i> | <i>PO 1</i> | <b>05</b>    |

Fig 2a

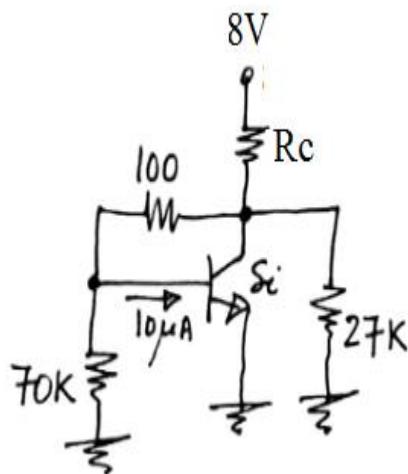

Fig 2b

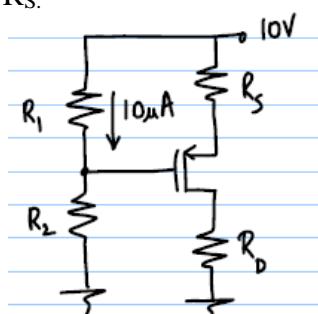

b) Determine the value of  $R_C$  in the circuit shown in Fig 2b. The base current of the silicon transistor was found to be  $10\mu A$  and  $\beta=41$ .

c) With a neat circuit explain the operation of series and parallel clippers

### UNIT - II

3 a) Determine the lower cut off frequency for the network of Fig.3a using the following parameters. Comment on the impact of the capacitance in low frequency.

$C_S = 10 \mu F$ ,  $C_E = 20 \mu F$ ,  $C_C = 1 \mu F$ ,  $R_S = 1 k\Omega$ ,  $R_1 = 40 k\Omega$ ,  $R_2 = 10 k\Omega$ ,  $R_E = 2 k\Omega$ ,  $R_C = 4 k\Omega$ ,  $R_L = 2.2 k\Omega$

Fig 3a

b) Suggest a suitable feedback circuit to obtain a high input impedance and low output impedance with unity gain. Also deduce expressions for voltage gain, input impedance and output impedance using a suitable model. Write any two applications of the same.

### OR

4 a) Find voltage gain, input impedance  $R_i$ , output impedance  $R_o$  and higher cut off frequencies for the circuit shown in Fig 4a. The transistor has  $\beta=99$ . Assume  $C_{be}=50pF$ ,  $C_{bc}=5pF$  and  $r_0=\infty$ .

CO 2 PO 1 05

CO 1 - 10

CO 2 PO 1 10

CO 2 PO 1 10

CO 2 PO 1 10

Fig 4a

b) Find the voltage gain, input and output impedance with feedback for voltage series feedback having  $A=-90$ ,  $R_i=15\text{ k}\Omega$ ,  $R_o=20\text{ k}\Omega$  for feedback of: i)  $\beta = -0.2$  ii)  $\beta = -0.75$

Comment on the results.

c) Derive an expression for input and output impedance of a current series feedback amplifier. "A" is the open loop gain of the amplifier and " $\beta$ " is the feedback factor.

### UNIT - III

5 a) Realize a power amplifier with Q point in cut off region and a suitable circuit arrangement to have a high efficiency without using a transformer. Also deduce an expression for theoretical efficiency and power dissipation with relevant waveforms.

b) Classify the different types of power amplifier and distinguish them based on efficiency, conduction angle of transistor, operating point and distortion.

c) A transformer coupled class A power amplifier supplies power to  $20\Omega$  load connected across the secondary of a step down transformer having a turns ratio of 5:1. Find the maximum power output for a zero signal collector current of 120mA.

### OR

6 a) Analyse the working and compare the maximum power efficiencies of a class A Series fed and transformer coupled power amplifiers. Deduce their efficiencies.

b) For a class B amplifier using a supply of  $V_{CC}=30\text{V}$  and driving a load of  $16\Omega$ , find the maximum input power, output power and transistor dissipation.

c) Find the total harmonic distortion for an output signal having fundamental amplitude of  $2.5\text{V}$ , second harmonic of amplitude  $0.25$ , third harmonic amplitude of  $0.1\text{V}$  and fourth harmonic amplitude of  $0.05\text{V}$

### UNIT - IV

7 a) Derive drain current expression for nMOSFET operating in (a) Triode region (b) Saturation region by drawing a neat cross section.

|   |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |    |

|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----|

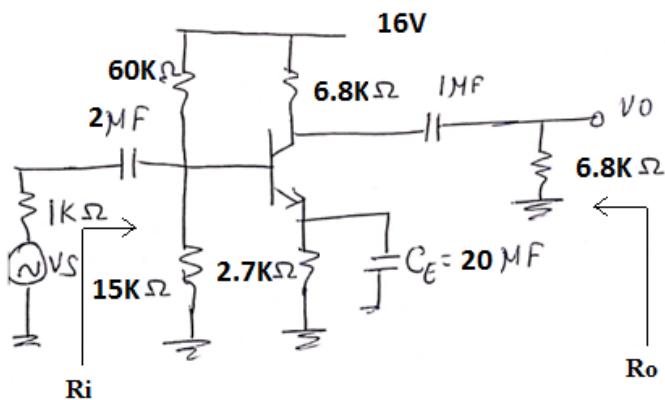

|   | b) | <p>(i) Calculate the drain current <math>I_D</math>, source voltage <math>V_S</math> and drain voltage <math>V_D</math> for the circuit shown in Fig 7b.</p> <p>(ii) Design the circuit if the source resistance is reduced to half its original value. Does the drain current double? Justify.</p>  <p>Fig 7b</p>                                                                                                                                                                            | CO 4 | PO 3 | 10 |

|   |    | <b>OR</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |    |

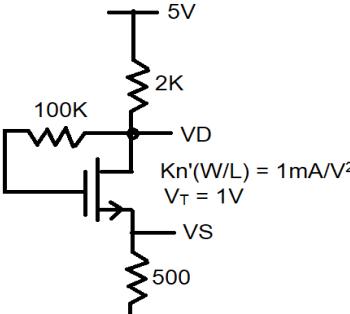

| 8 | a) | <p>In the circuit shown in Fig 8a, Calculate the value of <math>I_{DN}</math>, <math>I_{DP}</math> and <math>V_D</math> for (i) <math>V_i = 0V</math> (ii) <math>V_i = 2.5V</math> (iii) <math>V_i = -2.5V</math>. Assume <math>K_n'(W/L) = K_p'(W/L) = 1mA/V^2</math> , <math> V_T  = 1V</math> .</p>  <p>Fig 8a</p>                                                                                                                                                                        | CO 2 | PO 1 | 10 |

|   | b) | <p>Design the circuit in Fig 8b, so that PMOS device operates in saturation with <math>V_D</math> biased 1V away from the edge of triode region, with <math>I_D = 1mA</math>, and <math>V_D = 3V</math>. The device has <math>V_t = -0.9 V</math> and <math>\mu_p C_{ox} (W/L) = 0.25 \text{ mA/V}^2</math>. Specify the values of <math>V_G</math> , <math>V_D</math> , <math>V_S</math> , <math>R_1</math> , <math>R_2</math> , <math>R_D</math> and <math>R_S</math>.</p>  <p>Fig 8b</p> | CO 4 | PO 3 | 10 |

|   |    | <b>UNIT - V</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |    |

| 9 | a) | <p>Derive an expression for small-signal voltage gain, input impedance and output impedance for Common-Drain amplifier using small-signal equivalent circuit considering channel-length modulation. Deduce how this configuration can be used as</p>                                                                                                                                                                                                                                                                                                                           | CO 2 | PO 1 | 10 |

|    |    |                                                                                                                                                                                                                                                         |      |      |    |

|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----|

|    |    | Source-follower. Also, modify the expressions for no channel-length modulation.                                                                                                                                                                         |      |      |    |

|    | b) | Analyse the condition to have a minimum non-linear distortion in a MOS amplifier, Also obtain the equation for voltage gain in terms of $gm$ .                                                                                                          | CO 3 | PO 2 | 10 |

|    |    | <b>OR</b>                                                                                                                                                                                                                                               |      |      |    |

| 10 | a) | Obtain the expression for small signal voltage gain and output impedance of a Common Gate amplifier with resistive load, considering channel length modulation. Draw the circuit diagram and small signal equivalent circuit to obtain the expressions. | CO 2 | PO 1 | 10 |

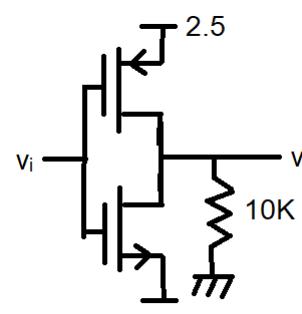

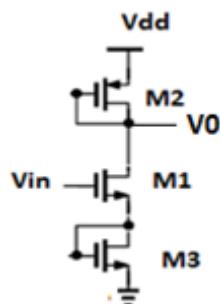

|    | b) | Analyse the circuit shown in Fig 10b draw a small signal model and derive equations for voltage gain and output impedance by considering Channel length modulation.                                                                                     | CO 3 | PO2  | 10 |

Fig 10b

\*\*\*\*\*