|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## January / February 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: III**

**Branch: Electronics and Communication Engineering**

**Duration: 3 hrs.**

**Course Code: 23EC3PCDCD**

**Max Marks: 100**

**Course: Digital Circuit Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

|                                                                                                                                                                                                       |   |    | <b>UNIT - I</b>                                                                                                                                                                                                                                             |             |              |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------|

|                                                                                                                                                                                                       |   |    | <b>CO</b>                                                                                                                                                                                                                                                   | <b>PO</b>   | <b>Marks</b> |           |

| <b>Important Note:</b> Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice. | 1 | a) | Express the function<br>i) $T = r(\bar{q} + s)(\bar{r} + \bar{q})$ into Maxterm canonical form<br>ii) $Y = \bar{a}bc + c\bar{d} + ac\bar{d}$ into Minterm canonical form                                                                                    | <b>CO 1</b> | <b>PO 1</b>  | <b>10</b> |

|                                                                                                                                                                                                       |   | b) | Determine minimal sum and minimal product using K-map<br>$f(a, b, c, d) = \sum m(1, 2, 3, 4, 9, 10) + \sum d(0, 14, 15)$                                                                                                                                    | <b>CO 1</b> | <b>PO 1</b>  | <b>10</b> |

|                                                                                                                                                                                                       |   |    | <b>OR</b>                                                                                                                                                                                                                                                   |             |              |           |

|                                                                                                                                                                                                       | 2 | a) | Given the logical equation $Y = ab + (a' + b')c + ab$<br>i) Simplify and realize the equation using NAND gates only<br>ii) Express the function as Standard SOP and Standard POS form<br>iii) Express the function as prime implicants and prime implicants | <b>CO 1</b> | <b>PO 1</b>  | <b>6</b>  |

|                                                                                                                                                                                                       |   | b) | Construct a combinational circuit that has 4-input and 1-output, indicates when numbers are divisible by 2 or 7.                                                                                                                                            | <b>CO 1</b> | <b>PO 1</b>  | <b>8</b>  |

|                                                                                                                                                                                                       |   | c) | Obtain minimal SOP expression using K-Map and realize the simplified expression using NAND gates only.<br>$f(w, x, y, z) = \sum m(0, 2, 3, 7, 8, 9, 10)$                                                                                                    | <b>CO 1</b> | <b>PO 1</b>  | <b>6</b>  |

| <b>UNIT - II</b>                                                                                                                                                                                      |   |    |                                                                                                                                                                                                                                                             |             |              |           |

|                                                                                                                                                                                                       | 3 | a) | Illustrate the functionality of Carry Look Ahead Adder                                                                                                                                                                                                      | <b>CO 1</b> | <b>PO 1</b>  | <b>10</b> |

|                                                                                                                                                                                                       |   | b) | Design Half Adder and Half Subtractor using 4:1 Mux.                                                                                                                                                                                                        | <b>CO 3</b> | <b>PO 3</b>  | <b>6</b>  |

|                                                                                                                                                                                                       |   | c) | Explain working of priority Encoder with necessary diagrams.                                                                                                                                                                                                | <b>CO 1</b> | <b>PO 1</b>  | <b>4</b>  |

|                                                                                                                                                                                                       |   |    | <b>OR</b>                                                                                                                                                                                                                                                   |             |              |           |

|                                                                                                                                                                                                       | 4 | a) | Realize Binary full adder and full Subtractor using 2:4 Decoder and NAND gate                                                                                                                                                                               | <b>CO 1</b> | <b>PO 1</b>  | <b>8</b>  |

|                                                                                                                                                                                                       |   | b) | Illustrate how PLA can be used for combinational logic design with reference to the functions. Assume 3X4X2 PLA is available.<br>$f_1(X, Y, Z) = \sum m(0, 1, 3, 4)$ $f_2(X, Y, Z) = \sum m(1, 2, 3, 4, 5)$ .                                               | <b>CO 3</b> | <b>PO 3</b>  | <b>6</b>  |

|                       |                    |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|-----|------|-----|-------------|-----|------------|-----|--------------------|--|--|--|

|                       | c)                 | Illustrate the functionality of ROM and PLA                                                                                                                                                                                                                                  | CO 1                  | PO 1      | 6   |      |     |             |     |            |     |                    |  |  |  |

|                       |                    | <b>UNIT - III</b>                                                                                                                                                                                                                                                            |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 5                     | a)                 | What is Race around condition? Explain how it is eliminated by using Master Slave JK Flip flop. Analyze your solution with appropriate logic diagrams. Also draw the waveforms.                                                                                              | CO 1                  | PO 1      | 10  |      |     |             |     |            |     |                    |  |  |  |

|                       | b)                 | Design a synchronous counter using JK Flip-flop to count the sequence 0-5-3-4-1-6-0 by obtaining minimal sum equations.                                                                                                                                                      | CO 3                  | PO 3      | 10  |      |     |             |     |            |     |                    |  |  |  |

|                       |                    | <b>OR</b>                                                                                                                                                                                                                                                                    |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 6                     | a)                 | Design and explain a 4 bit shift register using positive edge triggered D FF to operate as indicated in the table.                                                                                                                                                           | CO 3                  | PO 3      | 10  |      |     |             |     |            |     |                    |  |  |  |

|                       |                    | <table border="1"> <tr> <td>Mode Control<br/>S1 S0</td> <td>Operation</td> </tr> <tr> <td>0 0</td> <td>Hold</td> </tr> <tr> <td>0 1</td> <td>Shift Right</td> </tr> <tr> <td>1 0</td> <td>Shift Left</td> </tr> <tr> <td>1 1</td> <td>Parallel Operation</td> </tr> </table> | Mode Control<br>S1 S0 | Operation | 0 0 | Hold | 0 1 | Shift Right | 1 0 | Shift Left | 1 1 | Parallel Operation |  |  |  |

| Mode Control<br>S1 S0 | Operation          |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 0 0                   | Hold               |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 0 1                   | Shift Right        |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 1 0                   | Shift Left         |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 1 1                   | Parallel Operation |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

|                       | b)                 | Construct Mod 6 Synchronous Up Counter using J K Flip-flop with necessary tables and waveforms.                                                                                                                                                                              | CO 1                  | PO 1      | 10  |      |     |             |     |            |     |                    |  |  |  |

|                       |                    | <b>UNIT - IV</b>                                                                                                                                                                                                                                                             |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

| 7                     | a)                 | Analyze the sequential circuit given in Fig.7a                                                                                                                                                                                                                               | CO 2                  | PO 2      | 10  |      |     |             |     |            |     |                    |  |  |  |

|                       |                    |                                                                                                                                                                                                                                                                              |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

|                       |                    | Fig. 7a                                                                                                                                                                                                                                                                      |                       |           |     |      |     |             |     |            |     |                    |  |  |  |

|                       | b)                 | Design a synchronous circuit using positive edge triggered T-flip-flop to generate the following sequence 0-1-3-0 if input X=0 and 0-3-2-0 if input X=1. Provide an output to go high to indicate non-zero states irrespective of the sequence.                              | CO 3                  | PO 3      | 10  |      |     |             |     |            |     |                    |  |  |  |

|                 |    |                                                                                                                                                                                       | <b>OR</b> |             |             |           |

|-----------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-------------|-----------|

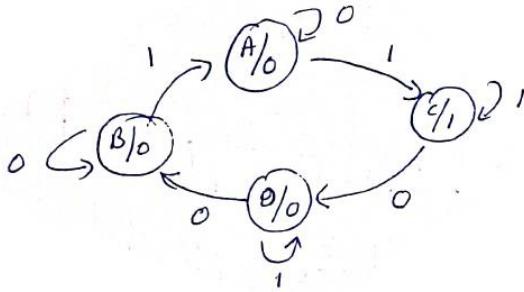

| 8               | a) | Analyse the state graph given in Fig 8a and realize the circuit using JK FF.                                                                                                          |           | <i>CO 2</i> | <i>PO 2</i> | <b>10</b> |

|                 |    | <br><b>Fig. 8a</b>                                                                                  |           |             |             |           |

| <b>UNIT - V</b> |    |                                                                                                                                                                                       |           |             |             |           |

| 9               | a) | Draw state diagram for Mealy state machine to detect sequence "1010" and also construct ASM chart for the same.                                                                       |           | <i>CO 2</i> | <i>PO 2</i> | <b>10</b> |

|                 | b) | Design an ASM chart for binary multiplier                                                                                                                                             |           | <i>CO 3</i> | <i>PO 3</i> | <b>10</b> |

| <b>OR</b>       |    |                                                                                                                                                                                       |           |             |             |           |

| 10              | a) | Construct an ASM chart for a synchronous sequential network that is to recognize the input sequence of pairs $x_1 x_2 = 01, 01, 11, 00$ . Output $z$ is to be 1 when $x_1 x_2 = 00$ . |           | <i>CO 2</i> | <i>PO 2</i> | <b>10</b> |

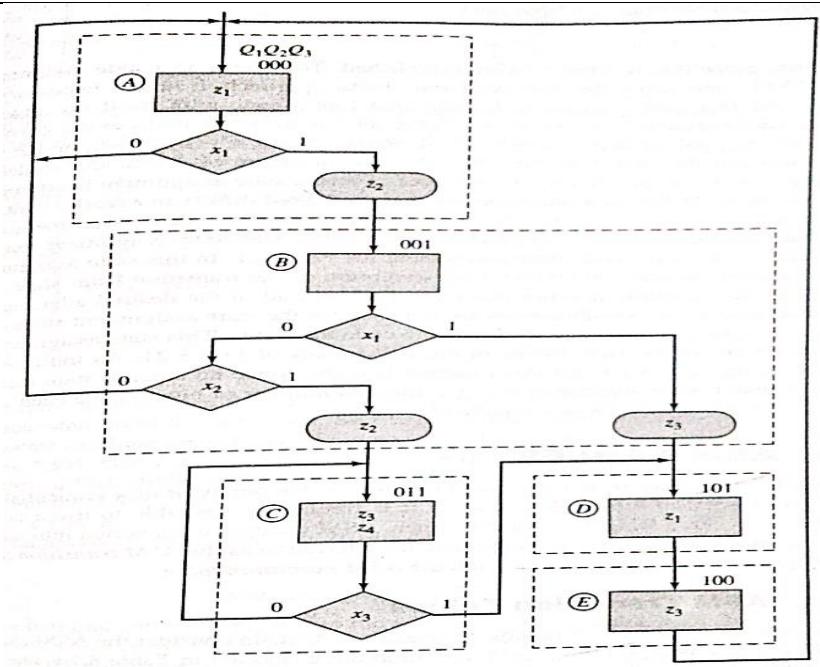

|                 | b) | Design circuit using D-flip flop for the given ASM chart.                                                                                                                             |           | <i>CO 3</i> | <i>PO 3</i> | <b>10</b> |

\*\*\*\*\*

B.M.S.C.E. - ODD SEM 2014-25