|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## April 2025 Semester End Make-Up Examinations

**Programme: B.E.**

**Semester: V**

**Branch: Electronics and Communication Engineering**

**Duration: 3 hrs.**

**Course Code: 23EC5PE1AD / 22EC5PE1AD**

**Max Marks: 100**

**Course: Advanced Digital Logic Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

|                                                                                                                                                                                                       |   |    | <b>UNIT - I</b>                                                                                                                                                                                                                                                 |  |  | <b>CO</b>   | <b>PO</b>   | <b>Marks</b> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|-------------|-------------|--------------|

| <b>Important Note:</b> Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice. | 1 | a) | Design and implement the asynchronous Mod-9 counter and develop the RTL with neat indentation, comments and header. For the counter module designed, develop the Verilog test bench which tests all possible test scenarios along with expected timing diagram. |  |  | <i>CO 3</i> | <i>PO 3</i> | <b>10</b>    |

|                                                                                                                                                                                                       |   | b) | Design and develop the Verilog source code for a 6:1 mux using 2:1 multiplexers.                                                                                                                                                                                |  |  | <i>CO 3</i> | <i>PO 3</i> | <b>10</b>    |

| <b>OR</b>                                                                                                                                                                                             |   |    |                                                                                                                                                                                                                                                                 |  |  |             |             |              |

|                                                                                                                                                                                                       | 2 | a) | Design and develop the Verilog source code for a 4-bit shift register. Use any modelling technique and verify the functionality using a test bench.                                                                                                             |  |  | <i>CO 3</i> | <i>PO 3</i> | <b>12</b>    |

|                                                                                                                                                                                                       |   | b) | Develop an example code in Verilog to illustrate full case and parallel case constructs.                                                                                                                                                                        |  |  | <i>CO 3</i> | <i>PO 3</i> | <b>08</b>    |

| <b>UNIT - II</b>                                                                                                                                                                                      |   |    |                                                                                                                                                                                                                                                                 |  |  |             |             |              |

|                                                                                                                                                                                                       | 3 | a) | Describe the guidelines that need to be followed while implementing Verilog RTL code.                                                                                                                                                                           |  |  | -           | -           | <b>10</b>    |

|                                                                                                                                                                                                       |   | b) | Analyse the different types of delay models for behavioural modelling.                                                                                                                                                                                          |  |  | <i>CO2</i>  | <i>PO2</i>  | <b>10</b>    |

| <b>OR</b>                                                                                                                                                                                             |   |    |                                                                                                                                                                                                                                                                 |  |  |             |             |              |

|                                                                                                                                                                                                       | 4 | a) | Analyse how the active events, inactive events, NBA update events, Monitor events and future events gets executed in a Verilog event queue.                                                                                                                     |  |  | <i>CO2</i>  | <i>PO2</i>  | <b>10</b>    |

|                                                                                                                                                                                                       |   | b) | What are Non-synthesizable Verilog constructs. List them.                                                                                                                                                                                                       |  |  | -           | -           | <b>10</b>    |

**UNIT - III**

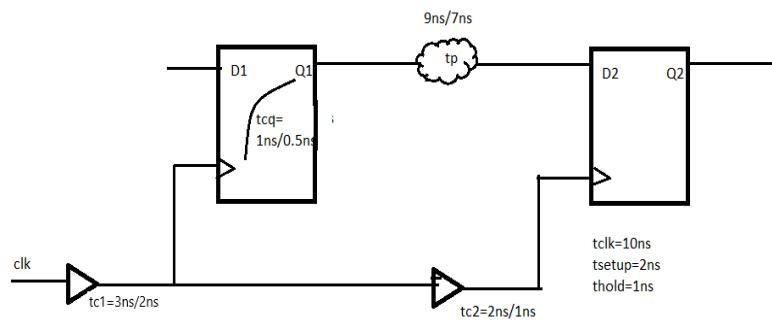

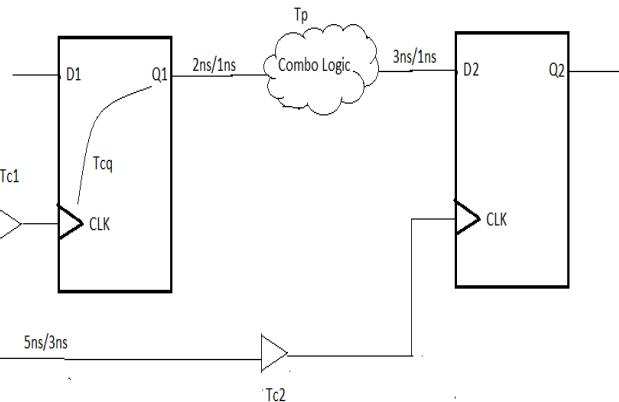

5 a) With neat labelled diagrams, analyse with equations, the setup time and hold time inequalities for the sequential circuit shown.

b) What is black hole time? Evaluate maximum frequency for a sequential circuit

**OR**

6 a) For the following figure, evaluate the setup time and hold time violations.

Given:  $T_{c1}=2\text{ns}/1\text{ns}$ ;  $T_{c2}=2\text{ns}/1\text{ns}$ ;  $T_p=9\text{ns}/7\text{ns}$ ;  $T_{cq}=4\text{ns}/3\text{ns}$ ;  $T_{setup}=2\text{ns}$ ;  $T_{hold}=1\text{ns}$ ;  $T_{clk}=6\text{ns}$ .

b) Discuss timing concepts with respect to set-up and Hold. Derive the Set-up and Hold inequalities.

*CO2 PO2 12*

*CO1 PO1 08*

*CO2 PO2 10*

*CO1 PO1 10*

|                 |    | <b>UNIT - IV</b>                                                                                                                                                                                                     |  |  |     |      |           |

|-----------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|-----|------|-----------|

| 7               | a) | What are standard cells? Discuss characterization goals and constraint driven optimization.                                                                                                                          |  |  | -   | -    | <b>12</b> |

|                 | b) | Develop the Verilog source code for JK flip flop using D flip flop.                                                                                                                                                  |  |  |     |      | <b>08</b> |

| <b>OR</b>       |    |                                                                                                                                                                                                                      |  |  |     |      |           |

| 8               | a) | Develop the Verilog source code for an overlapped Mealy FSM which detects 101 sequence and produces output as $y=1$ . Verify the functionality of the RTL by developing the test bench.                              |  |  | CO3 | PO 3 | <b>12</b> |

|                 | b) | Discuss the main optimization trade-offs. What are constraints and design goals?                                                                                                                                     |  |  |     |      | <b>08</b> |

| <b>UNIT - V</b> |    |                                                                                                                                                                                                                      |  |  |     |      |           |

| 9               | a) | Design and develop the Verilog source code for a non-overlapping Moore FSM which detects 001 or 100 sequences and produces output $y=1$ . Verify the functionality of the RTL by developing the test bench.          |  |  | CO3 | PO 3 | <b>14</b> |

|                 | b) | What is Cross domain crossing? Analyze the issues related to CDC designs.                                                                                                                                            |  |  |     |      | <b>06</b> |

| <b>OR</b>       |    |                                                                                                                                                                                                                      |  |  |     |      |           |

| 10              | a) | Draw the state diagram and develop the Verilog RTL for a Mealy state machine which produces output as '1' if the input bit stream detects 1111 sequence with overlap. Write the Verilog test bench to test the same. |  |  | CO3 | PO 3 | <b>12</b> |

|                 | b) | Analyze the condition for data loss in CDC designs with neat timing diagrams.                                                                                                                                        |  |  |     |      | <b>08</b> |

\*\*\*\*\*