|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## June 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: VI**

**Branch: Electronics & Communication Engineering**

**Duration: 3 hrs.**

**Course Code:16EC6DCMSD**

**Max Marks: 100**

**Course: Mixed Signal Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I  |    |                                                                                                                                                                                     | CO | PO | Marks     |

|-----------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-----------|

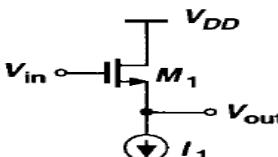

| 1         | a) | Analyze the given circuit to obtain $V_{out}$ if $(W/L)_1 = 20/0.5$ . $I_D = 200\mu A$ , $V_{th} = 0.6V$ , $\mu_n C_{ox} = 50 \mu A/ V^2$ , $V_{in} = 1.2V$                         | 2  | 2  | <b>10</b> |

|           |    | <br>Fig1                                                                                          |    |    |           |

|           | b) | Illustrate the working of common source amplifier with Resistive load                                                                                                               | 1  | 1  | <b>10</b> |

| <b>OR</b> |    |                                                                                                                                                                                     |    |    |           |

| 2         | a) | Deduce the representation of the minimum and maximum differential input voltage as well as common mode input voltage swing for a source-coupled Differential amplifier.             | 1  | 1  | <b>10</b> |

|           | b) | Perform the qualitative analysis of a differential pair circuit with the help of input output characteristics plots. Illustrate that small-signal gain is maximum for equal inputs. | 2  | 2  | <b>10</b> |

| UNIT - II |    |                                                                                                                                                                                     |    |    |           |

| 3         | a) | Implement a two stage opamp with single ended output and obtain the overall voltage gain starting with the simple two stage opamp                                                   | 1  | 1  | <b>10</b> |

|           | b) | Describe op amp design parameters also mention its importance.                                                                                                                      | 1  | 1  | <b>10</b> |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

| <b>OR</b>                                                                                               |    |                                                                                                                                                                                                                                                                          |   |   |           |

|---------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----------|

| 4                                                                                                       | a) | Highlight the drawbacks of a single stage Opamp and Show the implementation which can overcome the same.                                                                                                                                                                 | 1 | 1 | <b>10</b> |

|                                                                                                         | b) | Implement a two stage opamp with single ended output and obtain the overall voltage gain starting with the simple two stage opamp                                                                                                                                        | 1 | 1 | <b>10</b> |

| <b>UNIT - III</b>                                                                                       |    |                                                                                                                                                                                                                                                                          |   |   |           |

| 5                                                                                                       | a) | Analyze the linear model of type 1 PLL assuming under damped system and also obtain the expression for $\omega_{out}(t)$ , when the input is a frequency step.                                                                                                           | 2 | 2 | <b>10</b> |

|                                                                                                         | b) | Describe the various performance parameters of a VCO.                                                                                                                                                                                                                    | 1 | 1 | <b>10</b> |

| <b>OR</b>                                                                                               |    |                                                                                                                                                                                                                                                                          |   |   |           |

| 6                                                                                                       | a) | A VCO senses a sinusoidal control voltage $V_{cont} = V_m \cos \omega_m t$ , determine the output waveform and spectrum, justify your answer with appropriate description.                                                                                               | 2 | 2 | <b>10</b> |

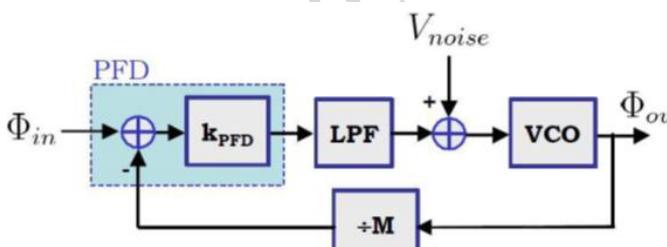

|                                                                                                         | b) | A linear model of a PLL with an active loop filter is shown in figure 2. Derive an expression for the transfer function of the VCO (i.e. $\phi_{out}/v_{out}$ , where $v_{out}$ and $\phi_{out}$ are the control voltage and the output phase of the VCO, respectively). | 1 | 1 | <b>10</b> |

| <br><b>Figure-2</b> |    |                                                                                                                                                                                                                                                                          |   |   |           |

| <b>UNIT - IV</b>                                                                                        |    |                                                                                                                                                                                                                                                                          |   |   |           |

| 7                                                                                                       | a) | In a 3 bit R-2R DAC if $R=1.1K\Omega$ and $2R=R_f=2K\Omega$ , determine the maximum INL and DNL for the converter. (Assume ideal case to be $R=1K\Omega$ ). Assume all the switches to be ideal and $V_{REF}=5V$ .                                                       | 2 | 2 | <b>10</b> |

|                                                                                                         | b) | Justify the need to address the Mixed Signal issues in chip design                                                                                                                                                                                                       | 1 | 1 | <b>10</b> |

| <b>OR</b>                                                                                               |    |                                                                                                                                                                                                                                                                          |   |   |           |

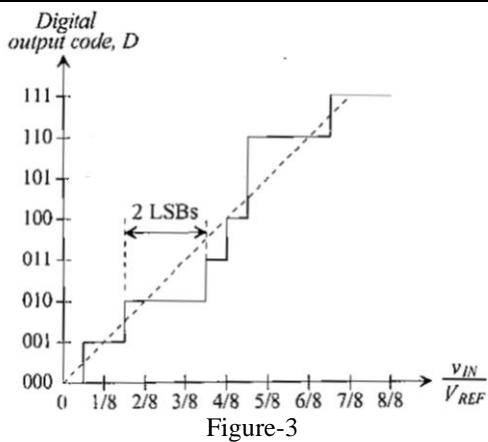

| 8                                                                                                       | a) | Identify different errors in Figure-3. Calculate DNL for each digital code and maximum resolution of the converter.                                                                                                                                                      | 1 | 1 | <b>10</b> |

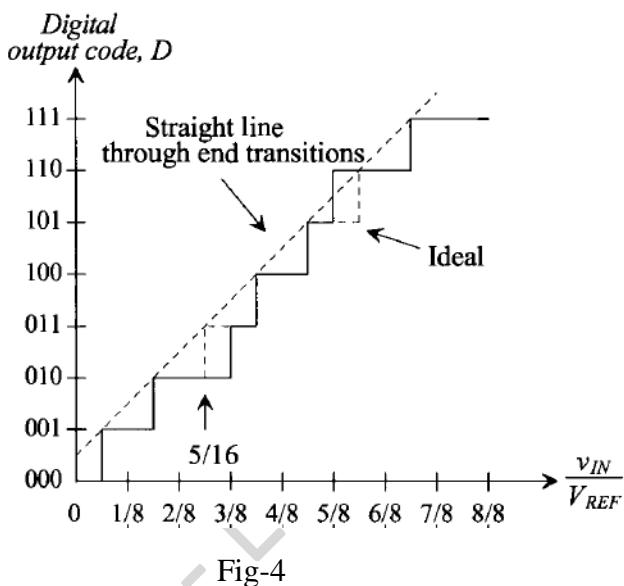

b) Determine the INL for the 3 bit ADC whose transfer curve is shown in Fig-4. Assume that  $V_{REF} = 5$  V. Draw the quantization error,  $Q_e$ , in units of LSBs.

### UNIT - V

9 a) Design a 3-bit DAC using an R-2R architecture with  $R = 1 \text{ k}\Omega$ ,  $R_F = 2\text{k}\Omega$ , and  $V_{REF} = 5\text{V}$ . Assume that the resistances of the switches are negligible. Determine the value of  $I_{TOT}$  for each digital input and the corresponding output voltage,  $V_{OUT}$ . Represent the same on a circuit and tabulate the output voltages.

b) Illustrate the working of a pipeline ADC. What are the advantages and drawbacks of the same?

### OR

10 a) Design a 3-bit charge-scaling DAC and find the value of the output voltage for  $D_2D_1D_0 = 010$  and  $101$ . Assume that  $V_{ref} = 5 \text{ V}$  and  $C = 0.5 \text{ pF}$ .

b) Illustrate the binary search operation in a Successive Approximation ADC with a suitable example.

\*\*\*\*\*