# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## June 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: VI**

**Branch: Electronics and Communication Engineering**

**Duration: 3 hrs.**

**Course Code: 19EC6PCMSD**

**Max Marks: 100**

**Course: MIXED SIGNAL DESIGN**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I  |    |                                                                                                                                                                                                                                                                                                                                                                                                | CO  | PO      | Marks     |

|-----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----------|

| 1         | a) | Obtain the small-signal voltage gain of a common source stage with resistive load with channel length modulation taken into account. Also draw the small-signal equivalent model.                                                                                                                                                                                                              | CO1 | PO<br>1 | <b>10</b> |

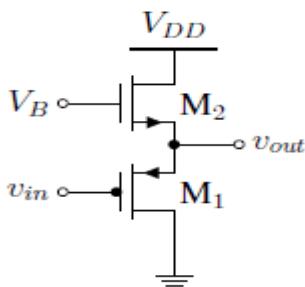

|           | b) | A source follower using NMOS current source shown in Figure which operates as a level shifter is designed to increase the output level by 1 V than the input level. Calculate the sizes of both the transistors if $ID1 = ID2 = 0.5$ mA; $VGS2 - VGS1 = 0.5$ V, $\mu nCox = 100 \mu A/V^2$ , $VTH = 0.7$ V, $\lambda = \gamma = 0$ .                                                           | CO1 | PO1     | <b>10</b> |

| <b>OR</b> |    |                                                                                                                                                                                                                                                                                                                                                                                                |     |         |           |

| 2         | a) | For the circuit shown in the Figure, if $(W/L) = 50/0.5$ , $R_D = 2$ k $\Omega$ , $\lambda = 0$ and $\mu nCox = 1.34225 \times 10^{-4}$ A/V $^2$ , $V_{th} = 0.7$ V, $V_{DD} = 3$ V.<br>(a) What is the small signal gain if $M_1$ is in saturation and $I_D = 1$ mA?<br>(b) What input voltage places $M_1$ at the edge of triode region? What is the small-signal gain under this condition? | CO1 | PO1     | <b>10</b> |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

|                  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |

|------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

|                  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |

|                  | b) | <p>Demonstrate that the Common-Source Common-Gate cascode amplifier has:</p> <ul style="list-style-type: none"> <li>(i) Superior gain compared to a common-source amplifier for same voltage swing</li> <li>(ii) smaller difference in drain currents due to a difference in drain voltages than without the stacking transistor (shielding property)</li> </ul>                                                                                                                                                                                                                                               | CO1 | PO1 |

| <b>UNIT - II</b> |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |

| 3                | a) | Perform the qualitative analysis of a differential pair circuit with the aid of input output characteristics plots. Illustrate that small-signal gain is maximum for equal inputs.                                                                                                                                                                                                                                                                                                                                                                                                                             | CO1 | PO1 |

|                  | b) | <p>A differential amplifier shown in Figure uses resistor than current source to define tail current of 1 mA. Assume <math>(W/L)_{1,2} = 25/0.5</math>, <math>\mu nCox = 50 \mu A/V^2</math>, <math>V_{TH} = 0.6 V</math>, <math>\lambda = \gamma = 0</math> and <math>V_{DD} = 3 V</math>.</p> <p>(a) What is the required input CM for which <math>R_{SS}</math> sustains 0.5 V?</p> <p>(b) Calculate <math>R_D</math> for a differential gain of 5.</p> <p>(c) What happens at the output if the input CM level is 50 mV higher than the value calculated in (a)?</p>                                       | CO2 | PO2 |

|                  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |

|                  |    | <b>OR</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |

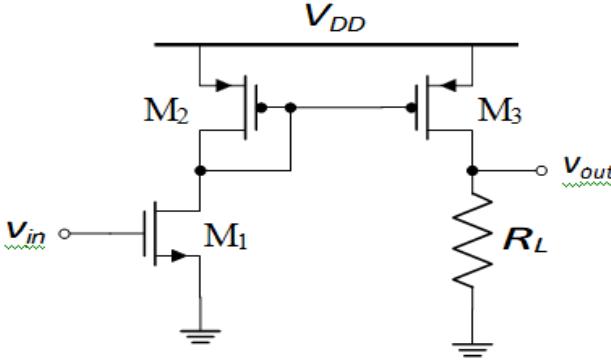

| 4                | a) | <p>Justify the need for current mirrors in integrated circuit design. Consider the circuit in the Figure with <math>R_L = 10 k\Omega</math>, <math>V_{DD} = 1.8 V</math> and NMOS (M1): <math>I_{D1} = 100 \mu A</math>, <math>(W/L)_1 = 50 \mu m/1 \mu m</math>, <math>\mu nCox = 120 \mu A/V^2</math>. PMOS (M2): <math>(W/L)_2 = 100 \mu m/1 \mu m</math>, <math>\mu pCox = 60 \mu A/V^2</math>.</p> <p>PMOS (M3): <math>(W/L)_3 = 100 \mu m/1 \mu m</math>, <math>\mu pCox = 60 \mu A/V^2</math>.</p> <p>Neglecting channel length modulation, determine</p> <p>(i) the output DC (or average) voltage</p> | CO1 | PO1 |

|                   |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |    |

|-------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

|                   |    | (ii) the small-signal voltage gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |    |

|                   |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |    |

|                   | b) | Perform the quantitative analysis of a differential pair circuit and calculate the differential output current. Indicate the variations of drain currents and the overall trans-conductance of differential pair versus input voltage.                                                                                                                                                                                                                                                                                                                                                                                  | CO1 | PO1 | 10 |

| <b>UNIT - III</b> |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |    |

| 5                 | a) | Design a telescopic cascode op-amp to satisfy the following specifications:<br>$V_{DD}=3V$ , differential output swing = 3 V, power dissipation = 10 mW, voltage gain = 1000. Assume $\mu nCox=60 \mu A V^2$ , $\mu pCox=30 \mu A V^2$ , $\lambda n=0.1 V^{-1}$ , $\lambda p=0.2 V^{-1}$ , $\gamma=0$ , $V_{TN}= V_{TP} =0.7 V$ .                                                                                                                                                                                                                                                                                       | CO3 | PO3 | 10 |

|                   | b) | With the help of neat circuit diagram and appropriate analyses, obtain the small-signal gain of a differential pair with current mirror load in differential and common-mode.                                                                                                                                                                                                                                                                                                                                                                                                                                           | CO2 | PO2 | 10 |

| <b>OR</b>         |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |    |

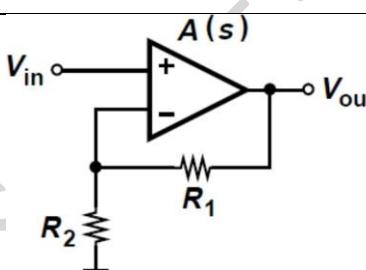

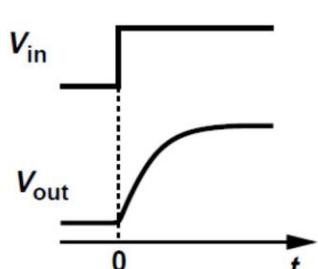

| 6                 | a) |   <p>In the circuit of Figure assume the Op-Amp is a single pole voltage amplifier. If <math>V_{in}</math> is a small step, calculate the time required for the output voltage to reach within 1% of its final value. What unity-gain bandwidth must the Op-Amp provide if <math>1 + R_1/R_2 \approx 10</math> and the settling time is to be less than 5 ns? For simplicity, assume that the low-frequency gain is much greater than unity.</p> | CO1 | PO1 | 10 |

|                   | b) | It is required to boost the output impedance of a differential cascode stage. Suggest a suitable circuit and illustrate how output impedance can be boosted substantially with appropriate description.                                                                                                                                                                                                                                                                                                                                                                                                                 | CO1 | PO1 | 10 |

| <b>UNIT - IV</b> |    |                                                                                                                                                                                                                                                                                          |            |            |           |  |

|------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------|--|

| 7                | a) | Realize a non-inverting amplifier using switched capacitors and explain its working.                                                                                                                                                                                                     | <i>CO3</i> | <i>PO3</i> | <b>7</b>  |  |

|                  | b) | Demonstrate the construction of an integrator using switched capacitor circuits. Draw its output waveform and write the output equation.                                                                                                                                                 | <i>CO1</i> | <i>PO1</i> | <b>6</b>  |  |

|                  | c) | Briefly discuss any two phenomena that affect the precision of sampled analog voltages.                                                                                                                                                                                                  | <i>CO1</i> | <i>PO1</i> | <b>7</b>  |  |

| <b>OR</b>        |    |                                                                                                                                                                                                                                                                                          |            |            |           |  |

| 8                | a) | With the help of neat circuit diagrams, demonstrate the operation of a multiply-by-two circuit in sampling mode and amplification mode.                                                                                                                                                  | <i>CO1</i> | <i>PO1</i> | <b>7</b>  |  |

|                  | b) | What is the need for common-mode feedback in fully differential amplifiers? Demonstrate how switched capacitors can be employed for it.                                                                                                                                                  | <i>CO1</i> | <i>PO1</i> | <b>8</b>  |  |

|                  | c) | Discuss the limitations of using a single NMOS and PMOS transistor as a sampling switch and how a transmission gate improves the performance.                                                                                                                                            | <i>CO1</i> | <i>PO1</i> | <b>5</b>  |  |

| <b>UNIT - V</b>  |    |                                                                                                                                                                                                                                                                                          |            |            |           |  |

| 9                | a) | Explain the principle of successive approximation. Assume that $V_{in} = 2.49$ V, $V_{REF} = 5$ V and 4-bit for the successive approximation ADC and that the comparator, because of its offset, makes the wrong decision for the MSB conversion. What will be the final digital output? | <i>CO3</i> | <i>PO3</i> | <b>10</b> |  |

|                  | b) | Discuss mixed signal layout issues.                                                                                                                                                                                                                                                      | <i>CO1</i> | <i>PO1</i> | <b>10</b> |  |

| <b>OR</b>        |    |                                                                                                                                                                                                                                                                                          |            |            |           |  |

| 10               | a) | Design a 3-bit charge-scaling DAC and find the value of the output voltage for $D_2D_1D_0 = 010$ and $110$ . Assume that $V_{REF} = 5$ V and $C = 0.5$ pF. Write the equation for the output voltage.                                                                                    | <i>CO3</i> | <i>PO3</i> | <b>8</b>  |  |

|                  | b) | Establish the relevance of the following terms with reference to ADC<br>(i) Quantization error (ii) Aliasing (iii) Offset error (iv) INL                                                                                                                                                 | <i>CO1</i> | <i>PO1</i> | <b>4</b>  |  |

|                  | c) | Explain the working of a single slope integrating ADC with the help of block diagram and discuss the accuracy issues related to the same.                                                                                                                                                | <i>CO1</i> | <i>PO1</i> | <b>8</b>  |  |