|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## February / March 2023 Semester End Main Examinations

**Programme: B.E.**

**Semester: V**

**Branch: Electronics and Instrumentation Engineering**

**Duration: 3 hrs.**

**Course Code: 19EI5PE2PT**

**Max Marks: 100**

**Course: Product Design Technology**

**Date: 01.03.2023**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

### UNIT - I

1 a) Describe the composition, cores and layers stack up for a basic PCB, multicore outer clad six-layer PCB. **10**

b) Elaborate on the functions of OrCAD Layout in the PCB Design Process. **10**

### UNIT - II

2 a) Discuss the manual board routing /editing mode tools and other indicators and controls available in Layout. **10**

b) Explain the classification and Types of PCB depending on performance, fabrication and assembly types and on land pattern density levels. **10**

### OR

3 a) Bring out a summary of new project design flow and its options in OrCAD capture. Also, discuss the types of OrCAD libraries available. **10**

b) Describe the registration, break out and annular ring control tolerances and standard board panel sizes of PCB. **10**

### UNIT - III

4 a) Describe the manual and reflow soldering process of mounting components on a PCB with neat schematic. **08**

b)

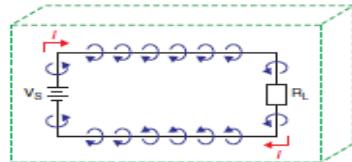

Relate to diagram shown and deliberate how to provide a low-impedance return path for power and signal lines and reduces unwanted cross talk to nearby conductors.

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

## OR

5 a) Discuss the guidelines for component placement and orientation guidelines. Also component spacing for integrated circuit through hole devices. **12**

b) Suggest a solution to overcome the problem of digital noise being injected into analog circuitry through the supply planes. **08**

## UNIT - IV

6 a) Explain the types of packing, pins types and their attributes when making parts in capture. **10**

b) Describe the steps for basic footprint design process using layout. **10**

## UNIT - V

7 a)  **10**

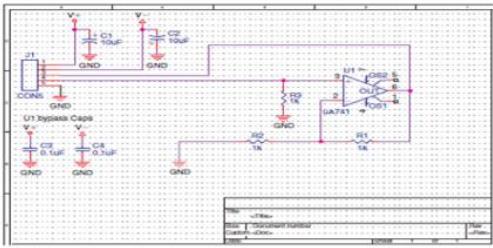

For the analog circuit shown, discuss steps to set up the design in capture and generate a .MNL file for layout.

b) Discuss the steps for generating Bill of Materials for a given PCB design which is post processed using ORCAD. **10**

\*\*\*\*\*