# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## April 2024 Semester End Main Examinations

**Programme: B.E.**

**Semester: III**

**Branch: Electronics and Telecommunication Engineering**

**Duration: 3 hrs.**

**Course Code: 23ET3PCALC**

**Max Marks: 100**

**Course: Analog and Linear Circuits**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>  |    |                                                                                                                                                                                                                                                              | <b>CO</b>    | <b>PO</b>       | <b>Marks</b> |

|------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------|

| 1                | a) | Explain the design constraint of classical discrete-circuit biasing arrangement with circuit and relevant equations and also explain how does $R_E$ provide a negative feedback action to stabilize the bias current.                                        | <i>CO1,2</i> | <i>PO1, 2,3</i> | <b>08</b>    |

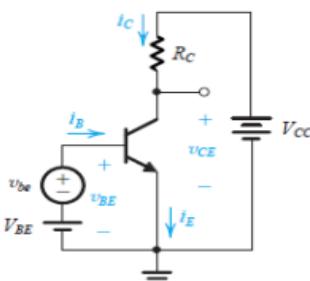

|                  | b) | Calculate the voltage gain of the circuit shown in Fig. 1b for $v_{be} = 0.005 \cos \omega t$ V, also find $v_{ce}$ and $i_b$ , if $V_{BE}$ is adjusted to yield a dc collector current of 1 mA, $V_{CC} = 15$ V, $R_C = 5$ k $\Omega$ , and $\beta = 100$ . | <i>CO1,2</i> | <i>PO1,2,3</i>  | <b>08</b>    |

|                  | c) | <br><b>Fig. 1b</b>                                                                                                                                                        | <i>CO1,2</i> | <i>PO1,2,3</i>  | <b>04</b>    |

| <b>UNIT - II</b> |    |                                                                                                                                                                                                                                                              |              |                 |              |

| 2                | a) | Prove the following properties of Negative feedback: (a) Gain Desensitivity (b) Bandwidth Extension                                                                                                                                                          | <i>CO1,2</i> | <i>PO1,2,3</i>  | <b>10</b>    |

|                  | b) | Derive the expression of Gain, Input-Resistance, and Output-resistance for voltage amplifier with the help of a neat circuit diagram and explanation.                                                                                                        | <i>CO1,2</i> | <i>PO1,2,3</i>  | <b>10</b>    |

| <b>OR</b>        |    |                                                                                                                                                                                                                                                              |              |                 |              |

| 3                | a) | Derive the expression of power-conversion efficiency of Class A amplifier with the help of a neat circuit diagram and explanation.                                                                                                                           | <i>CO1,2</i> | <i>PO1,2,3</i>  | <b>10</b>    |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

|   |    |                                                                                                                                                                                                                                                                                                                    |       |         |           |

|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-----------|

|   | b) | Derive the expression of power-conversion efficiency of Class B amplifier with the help of a neat circuit diagram and explanation.                                                                                                                                                                                 | CO1,2 | PO1,2,3 | <b>10</b> |

|   |    | <b>UNIT - III</b>                                                                                                                                                                                                                                                                                                  |       |         |           |

| 4 | a) | Explain the effects of Biasing by Fixing $V_{GS}$ in a MOSFET with $i_D-V_{GS}$ characteristic.                                                                                                                                                                                                                    | CO1,2 | PO1,2,3 | <b>08</b> |

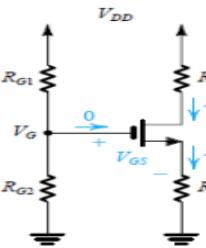

|   | b) | Design the circuit of Fig. 3b to establish a dc drain current $I_D = 0.5$ mA. The MOSFET is specified to have $V_t = 1$ V and $(kn' W/L) = 1$ mA/V <sup>2</sup> . For simplicity, neglect the channel-length modulation effect (i.e., assume $\lambda = 0$ ). Use a power-supply $V_{DD} = 15$ V. $I_g = 1\mu A$ . | CO1,2 | PO1,2,3 | <b>08</b> |

|   |    |  <p>Fig.3b</p>                                                                                                                                                                                                                    |       |         |           |

|   | c) | Explain with a neat circuit diagram the Biasing of MOSFET using a Drain-to-Gate Feedback Resistor.                                                                                                                                                                                                                 | CO1,2 | PO1,2,3 | <b>04</b> |

|   |    | <b>UNIT - IV</b>                                                                                                                                                                                                                                                                                                   |       |         |           |

| 5 | a) | Explain positive and negative half wave precision rectifier with the help of neat circuit diagrams and relevant waveforms.                                                                                                                                                                                         | CO3,4 | PO1,2,3 | <b>10</b> |

|   | b) | Explain with a neat circuit diagram Instrumentation Amplifier Using Transducer Bridge.                                                                                                                                                                                                                             | CO3,4 | PO1,2,3 | <b>10</b> |

|   |    | <b>UNIT - V</b>                                                                                                                                                                                                                                                                                                    |       |         |           |

| 6 | a) | Explain the DAC using R-2R ladder with the help of a neat circuit diagram.                                                                                                                                                                                                                                         | CO3,4 | PO1,2,3 | <b>10</b> |

|   | b) | Explain the internal block diagram of 555 timer with a neat diagram.                                                                                                                                                                                                                                               | CO3,4 | PO1,2,3 | <b>10</b> |

|   |    | <b>OR</b>                                                                                                                                                                                                                                                                                                          |       |         |           |

| 7 | a) | Explain the ADC using the Successive-approximation method with the help of a neat circuit diagram.                                                                                                                                                                                                                 | CO3,4 | PO1,2,3 | <b>10</b> |

|   | b) | Explain with a neat circuit diagram the working of a Monostable Multivibrator.                                                                                                                                                                                                                                     | CO3,4 | PO1,2,3 | <b>10</b> |

\*\*\*\*\*