|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## June 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: IV**

**Branch: Electronics & Telecommunication Engineering**

**Duration: 3 hrs.**

**Course Code: 19ET4PCVLD**

**Max Marks: 100**

**Course: VLSI Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>  |    |                                                                                                                                                                                | <b>CO</b>  | <b>PO</b>  | <b>Marks</b> |

|------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|

| 1                | a) | Define Moore's first law with an appropriate graph and thereby explain its implication.                                                                                        | <i>CO1</i> |            | <b>04</b>    |

|                  | b) | With neat sketches, analyze the nMOS fabrication technique. Clearly describe the various masking operations performed.                                                         | <i>CO1</i> |            | <b>08</b>    |

|                  | c) | Design and implement the logic function, $Y = (A+B) \cdot C$ using minimum number of transistors. Use CMOS technology for implementation and thereby sketch the stick diagram. | <i>CO3</i> | <i>PO3</i> | <b>08</b>    |

| <b>OR</b>        |    |                                                                                                                                                                                |            |            |              |

| 2                | a) | Compare CMOS and Bipolar technologies.                                                                                                                                         | <i>CO1</i> |            | <b>04</b>    |

|                  | b) | Analyze with relevant diagrams and masking operations, the p-well fabrication process.                                                                                         | <i>CO2</i> | <i>PO1</i> | <b>08</b>    |

|                  | c) | Using minimum number of transistors, design the logic function $Y = (A+BC)$ and thereby implement the same using monochrome layout diagram.                                    | <i>CO2</i> | <i>PO1</i> | <b>08</b>    |

| <b>UNIT - II</b> |    |                                                                                                                                                                                |            |            |              |

| 3                | a) | Design a circuit for the expression $Y = \overline{A} + BC$ through CVSL technology and explain the advantages of CVSL technology.                                             | <i>CO3</i> | <i>PO3</i> | <b>10</b>    |

|                  | b) | Design a RS latch dynamic CMOS circuit and analyze its working principle and thereby sketch its stick diagram.                                                                 | <i>CO3</i> | <i>PO3</i> | <b>10</b>    |

| <b>OR</b>        |    |                                                                                                                                                                                |            |            |              |

| 4                | a) | Design a 3-input OR gate using C <sup>2</sup> MOS logic and analyze its working principle. Also sketch the stick diagram for the circuit.                                      | <i>CO3</i> | <i>PO3</i> | <b>10</b>    |

|                  | b) | Design a 4:1 Mux using Transmission gate and analyze its working principle. Also sketch the stick diagram for a 2:1 Mux circuit.                                               | <i>CO3</i> | <i>PO3</i> | <b>10</b>    |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

| <b>UNIT - III</b> |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

|-------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 5                 | a)                                                                                   | Derive the expressions for rise – time estimation and fall – time estimation of a CMOS inverter with relevant terminologies.                                                                                                                                                                                                                                                                                                                                         | CO2 | PO1 | <b>06</b> |

|                   | b)                                                                                   | Explain the basic architectural guidelines considered in VLSI design.                                                                                                                                                                                                                                                                                                                                                                                                | CO1 |     | <b>04</b> |

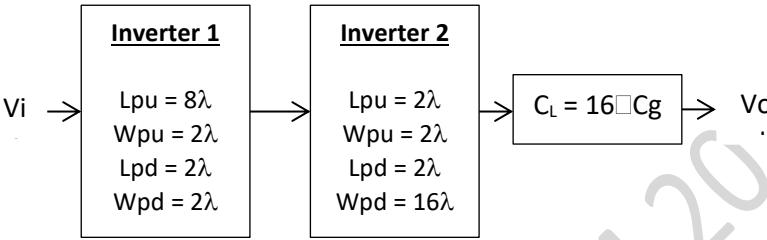

|                   | c)                                                                                   | <p>Two nMOS inverters are cascaded as shown in Fig below. Calculate the delay in terms of <math>\tau</math>. <math>C_1 = 4\lambda C_g</math> at the output of first inverter, hence analyze:</p> <p>(i) The delay if <math>\tau = 0.4</math> ns</p> <p>(ii) If due to connecting wires, the stray capacitance increases by <math>4\lambda C_g</math>, what is the delay time?</p>  | CO3 | PO4 | <b>10</b> |

| <b>OR</b>         |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

| 6                 | a)                                                                                   | Prove that the total time constant is 0.7 ns for a CMOS inverter and 0.5 ns for an nMOS inverter. Use appropriate terminologies and equivalent circuits for your analysis.                                                                                                                                                                                                                                                                                           | CO3 | PO2 | <b>10</b> |

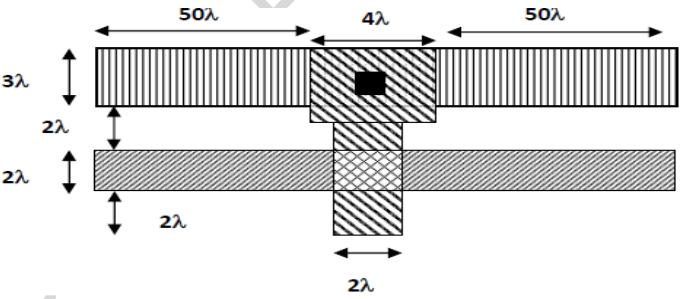

|                   | b)                                                                                   | Determine the total capacitance between the following area and substrate in the figure given below. Consider 5μm technology for your calculations.                                                                                                                                                                                                                                                                                                                   | CO3 | PO2 | <b>10</b> |

|                   |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

| <b>UNIT - IV</b>  |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

| 7                 | a)                                                                                   | Design and analyze the following:<br>i. 4-bit combinational shifter<br>ii. 4 X 4 barrel shifter                                                                                                                                                                                                                                                                                                                                                                      | CO3 | PO3 | <b>10</b> |

|                   | b)                                                                                   | Design and analyze with relevant diagrams a Manchester carry chain adder and also write the stick diagram for a 1-bit Manchester chain.                                                                                                                                                                                                                                                                                                                              | CO3 | PO3 | <b>10</b> |

| <b>OR</b>         |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

| 8                 | a)                                                                                   | Design and analyze the following:<br>i. 4 bit SISO dynamic register<br>ii. 4 X 4 cross bar switch                                                                                                                                                                                                                                                                                                                                                                    | CO3 | PO3 | <b>10</b> |

|    |    |                                                                                                                                                                                                                                                                                                                 |     |     |           |

|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|    | b) | Design and analyze with relevant diagrams a Serial-Parallel multiplier. Consider an example for your analysis.                                                                                                                                                                                                  | CO3 | PO3 | <b>10</b> |

|    |    | <b>UNIT - V</b>                                                                                                                                                                                                                                                                                                 |     |     |           |

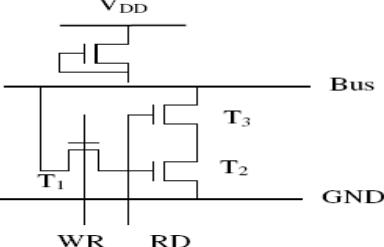

| 9  | a) | Identify the memory device in figure below and thereby explain its operation.                                                                                                                                                                                                                                   | CO2 | PO1 | <b>03</b> |

|    |    |                                                                                                                                                                                                                                |     |     |           |

|    | b) | Analyze the practical design issues of testability with respect to the following: <ol style="list-style-type: none"> <li>Controllability and Observability</li> <li>Gated Clocks</li> <li>Redundant Logic</li> </ol>                                                                                            | CO2 | PO1 | <b>07</b> |

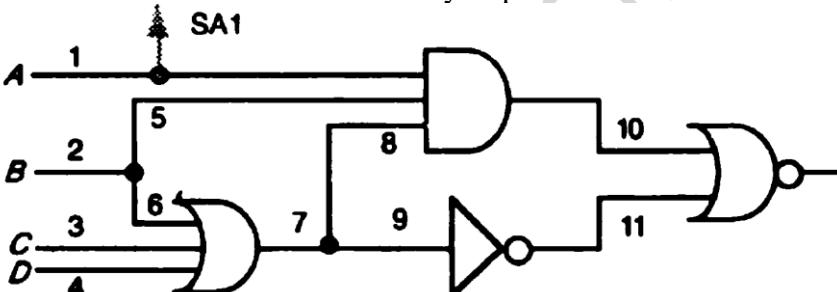

|    | c) | For the circuit given below in figure below consider a <ol style="list-style-type: none"> <li>SA1 at line 1 and thereby implement the test vectors</li> <li>SA1 at line 8 and thereby implement the test vectors</li> </ol>  | CO3 | PO4 | <b>10</b> |

|    |    | <b>OR</b>                                                                                                                                                                                                                                                                                                       |     |     |           |

| 10 | a) | Analyze the following practical design issues in VLSI testing environment: <ol style="list-style-type: none"> <li>Use of Bus structures</li> <li>Self – Reset Logic</li> <li>BILBO testing</li> </ol>                                                                                                           | CO4 | PO2 | <b>10</b> |

|    | b) | Implement and analyze the following memory cells. Sketch the equivalent stick diagrams. <ol style="list-style-type: none"> <li>3T Dynamic RAM cell</li> <li>Pseudo static memory cell</li> </ol>                                                                                                                | CO4 | PO2 | <b>10</b> |

\*\*\*\*\*