|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## June / July 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: V**

**Branch: Electronics & Telecommunication Engineering**

**Duration: 3 hrs.**

**Course Code: 23ET5PE1DD / 22ET5PE1DD**

**Max Marks: 100**

**Course: DIGITAL SYSTEM DESIGN**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I  |    |                                                                                                                                                                                                       | CO  | PO  | Marks     |

|-----------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 1         | a) | Design a Full Adder using a suitable decoder and hence describe the behavior in Verilog HDL                                                                                                           | CO3 | PO3 | <b>06</b> |

|           | b) | Design a BCD to Excess-3 code converter using sequential logic with Verilog                                                                                                                           | CO3 | PO3 | <b>08</b> |

|           | c) | Analyze the following operations and design using Verilog HDL                                                                                                                                         | CO3 | PO3 | <b>06</b> |

| <b>OR</b> |    |                                                                                                                                                                                                       |     |     |           |

| 2         | a) | Convert the following Mealy FSM to Moore FSM                                                                                                                                                          | CO2 | PO2 | <b>06</b> |

|           |    | <pre> graph LR     q0((q0)) -- "b/0" --&gt; q0     q0 -- "a/0" --&gt; q1((q1))     q1 -- "a/0" --&gt; q1     q1 -- "b/1" --&gt; q2((q2))     q2 -- "b/0" --&gt; q2     q2 -- "a/0" --&gt; q1   </pre> |     |     |           |

|           | b) | Write a Verilog model of the Mealy FSM described by the state diagram with a test bench                                                                                                               | CO3 | PO3 | <b>06</b> |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

|   |    |                                                                                                                                                                                                                                                                                                                                         |     |     |    |

|---|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

|   |    |                                                                                                                                                                                                                                                                                                                                         |     |     |    |

|   | c) | Design a synchronous counter using D-FFs for the sequence 0, 1, 2, 4, 6, 0 and hence describe the behavior in Verilog HDL                                                                                                                                                                                                               | CO3 | PO3 | 08 |

|   |    | <b>UNIT - II</b>                                                                                                                                                                                                                                                                                                                        |     |     |    |

| 3 | a) | Explain Synthesis process with flow chart                                                                                                                                                                                                                                                                                               | CO1 | PO1 | 04 |

|   | b) | Design a switch level diagram for the function $Y = \overline{(A + B)(C + D)E}$ and hence describe the behavior in Verilog                                                                                                                                                                                                              | CO2 | PO2 | 06 |

|   | c) | For the following code obtain gate level synthesis<br><br><pre>module example (a, y); input [2:0]a; output [3:0]y; reg y; always@ (a) begin if (a&lt;3'b101) y=2*a +5; end endmodule</pre>                                                                                                                                              | CO3 | PO3 | 10 |

|   |    | <b>OR</b>                                                                                                                                                                                                                                                                                                                               |     |     |    |

| 4 | a) | Design a D-FF using minimum number of transistors and hence describe the behavior in Verilog HDL                                                                                                                                                                                                                                        | CO3 | PO3 | 06 |

|   | b) | Design a 2-to-1 multiplexer using bufif0 and bufif1 gates and hence describe the Verilog behavior                                                                                                                                                                                                                                       | CO2 | PO2 | 04 |

|   | c) | Analyze the following Verilog process and give the circuit generated by the code 8M<br><br><pre>module syn (clk,clr,Dout, Din,load); input clk,clr; input [3:0] Din; output reg [3:0] Dout; always @ (posedge clk or posedge clr) begin if (clr == 1'b1)      Dout &lt;= 4'b0; else if (load ==1'b1) Dout &lt;=Din; end endmodule</pre> | CO3 | PO3 | 10 |

|   |    | <b>UNIT - III</b>                                                                                                                                                                                                                                                                                                                       |     |     |    |

| 5 | a) | List the steps for designing a digital system with FPGA                                                                                                                                                                                                                                                                                 | CO1 | PO1 | 04 |

|   |    |                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |           |

|---|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|   | b) | Realize a 2-bit binary counter using Xilinx 3000 series OR Xilinx 4000 series device                                                                                                                                                                                                                                                                                                                                                  | CO2 | PO2 | <b>08</b> |

|   | c) | Realize the following functions using PLA<br><br>$F1 (A,B,C,D) = \sum m(2,3,5,7,8,9,10,11,13,15)$<br>$F2 (A,B,C,D) = \sum m(2,3,5,6,7,10,11,14,15)$<br>$F3 (A,B,C,D) = \sum m(6,7,8,9,13,14,15)$                                                                                                                                                                                                                                      | CO2 | PO2 | <b>08</b> |

|   |    | <b>OR</b>                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |

| 6 | a) | Briefly explain the operation of ALTERA 7000 series CPLD                                                                                                                                                                                                                                                                                                                                                                              | CO1 | PO1 | <b>08</b> |

|   | b) | Realize the following functions using a suitable PAL<br><br>$Q_1^+ = A' B Q_1 + A' B' Q_2$<br>$Q_2^+ = A Q_2 + B' Q_1$                                                                                                                                                                                                                                                                                                                | CO2 | PO2 | <b>08</b> |

|   | c) | With a neat diagram explain the operation of I/O block in 3000 series FPGA                                                                                                                                                                                                                                                                                                                                                            | CO1 | PO1 | <b>04</b> |

|   |    | <b>UNIT - IV</b>                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

| 7 | a) | Design and draw the gate level diagram and hence write the Verilog code for 2-bit X 2-bit Combinational Array Multiplier. Also write the stimulus block                                                                                                                                                                                                                                                                               | CO3 | PO3 | <b>10</b> |

|   | b) | With a neat block diagram explain the operation of serial adder with accumulator                                                                                                                                                                                                                                                                                                                                                      | CO1 | PO1 | <b>05</b> |

|   | c) | Draw the state graph for binary divider which divides 8-bit dividend to 4-bit divisor                                                                                                                                                                                                                                                                                                                                                 | CO2 | PO2 | <b>05</b> |

|   |    | <b>OR</b>                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |           |

| 8 | a) | Draw the state graph and hence write a Verilog code for 4-bit X 4-bit unsigned Binary multiplier                                                                                                                                                                                                                                                                                                                                      | CO3 | PO3 | <b>08</b> |

|   | b) | Write a Verilog code for 4-bit carry look ahead adder                                                                                                                                                                                                                                                                                                                                                                                 | CO3 | PO3 | <b>04</b> |

|   | c) | Write state graph and Verilog description of a traffic light controller for the intersection of street A and street B with the following conditions:<br>i. When A is green, it remains green at least 50sec, and then the lights changes only when a vehicle approaches on B.<br>ii. When B is green, it remains in green at least 40sec, and then the lights change back unless there is a vehicle on street B and none on street A. | CO3 | PO3 | <b>08</b> |

|   |    | <b>UNIT - V</b>                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |           |

| 9 | a) | Draw an SM chart for half adder                                                                                                                                                                                                                                                                                                                                                                                                       | CO2 | PO2 | <b>05</b> |

|   | b) | Explain the concept of linked state machines                                                                                                                                                                                                                                                                                                                                                                                          | CO1 | PO1 | <b>05</b> |

|   | c) | Draw an SM chart and hence write a Verilog code for 4-bit multiplier control network                                                                                                                                                                                                                                                                                                                                                  | CO3 | PO3 | <b>10</b> |

| <b>OR</b> |    |    |                                                                        |     |               |

|-----------|----|----|------------------------------------------------------------------------|-----|---------------|

|           | 10 | a) | Realize SM chart and hence write Verilog code for Dice game controller | CO3 | PO3 <b>10</b> |

|           |    | b) | Explain the concept of microprogramming                                | CO3 | PO1 <b>05</b> |

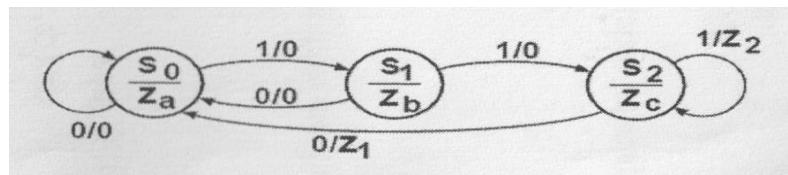

|           |    | c) | Convert the following state diagram to state machine chart.            | CO3 | PO2 <b>05</b> |

\*\*\*\*\*

REAPPEAR EXAMS 2024-25