# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## January / February 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: V**

**Branch: Electronics & Telecommunication Engineering**

**Duration: 3 hrs.**

**Course Code: 23ET5PCFLI**

**Max Marks: 100**

**Course: FUNDAMENTALS OF VLSI**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>  |    |                                                                                                                                                                            | <b>CO</b> | <b>PO</b> | <b>Marks</b> |

|------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|--------------|

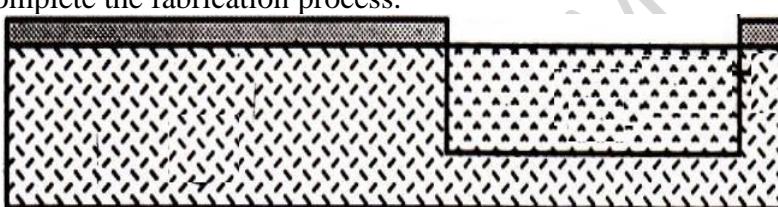

| 1                | a) | Considering the initial process of fabrication given below, complete the fabrication process.                                                                              | CO2       | PO1       | 10           |

|                  | b) | Design and implement a CMOS circuit for the expression $Y = A + BC$ using minimum number of transistors. Also implement its Stick diagram.                                 | CO3       | PO3       | 10           |

| <b>OR</b>        |    |                                                                                                                                                                            |           |           |              |

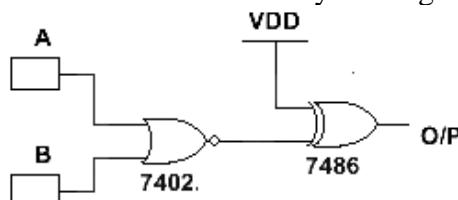

| 2                | a) | Design and implement the circuit shown below using minimum number of transistors. Use CMOS technology for implementation and thereby sketch the Monochrome layout diagram. | CO3       | PO3       | 10           |

|                  | b) | Analyze with relevant diagrams and masking operations, the CMOS twin tub fabrication process.                                                                              | CO1       | -         | 10           |

| <b>UNIT - II</b> |    |                                                                                                                                                                            |           |           |              |

| 3                | a) | Design a 3 input OR gate using C <sup>2</sup> MOS logic and analyze its working principle. Also sketch the stick diagram for the circuit.                                  | CO3       | PO3       | 14           |

|                  | b) | Interpret the output of the following circuit shown below and write the output expression and its stick diagram.                                                           | CO3       | PO2       | 06           |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

**OR**

|                    |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |           |

|--------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 4                  | a) | Design, analyze and implement a Dynamic CMOS circuit for a 3 input NOR gate with minimum number of transistors. Also sketch the stick diagram for the same.                                                                                                                                                                                                                                                                                      | CO3 | PO3 | <b>14</b> |

|                    | b) | Design a 4:1 Mux using Transmission gate and write its functional table. Also sketch the stick diagram for a 2:1 Mux circuit.                                                                                                                                                                                                                                                                                                                    | CO3 | PO3 | <b>06</b> |

| <b>UNIT - III</b>  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |           |

| 5                  | a) | Derive the expressions for rise – time estimation and fall – time estimation of a CMOS inverter with relevant terminologies.                                                                                                                                                                                                                                                                                                                     | CO2 | PO1 | <b>05</b> |

|                    | b) | Analyze the basic architectural guidelines considered in VLSI design.                                                                                                                                                                                                                                                                                                                                                                            | CO1 | -   | <b>05</b> |

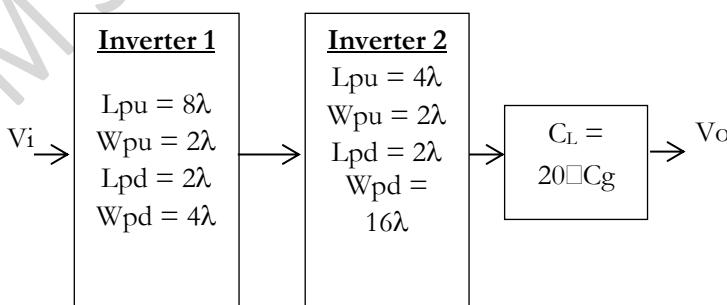

|                    | c) | <p>Two nMOS inverters are cascaded as shown in Fig below. Calculate the delay in terms of <math>\tau</math>. If <math>C_L = 8\lambda C_g</math> at the output of first inverter, determine:</p> <p>(i) The delay if <math>\tau = 0.6</math> ns?</p> <p>(ii) If due to connecting wires, the stray capacitance increases by <math>8\lambda C_g</math>, what is the delay time?</p> <p>(iii) Implement the stick diagram of the nMOS inverter.</p> | CO3 | PO2 | <b>10</b> |

| <b>BMSC2024-25</b> |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |           |

**OR**

|   |    |                                                                                                                                                                                                       |     |     |           |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 6 | a) | Starting from the nMOS inverter characteristics, derive the expression for $Z_{pu}/Z_{pd}$ of an nMOS inverter driven by another nMOS inverter. Also analyze different nMOS inverter implementations. | CO2 | PO1 | <b>10</b> |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|   |    |                                                                                                                                                                                                                                                                                                                                                |     |     |    |

|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

|   | b) | <p>Determine the total capacitance between the following area and substrate in the figure given below. Consider <math>5\mu\text{m}</math> technology for your calculations.</p>                                                                                                                                                                | CO3 | PO2 | 10 |

|   |    | <b>UNIT - IV</b>                                                                                                                                                                                                                                                                                                                               |     |     |    |

| 7 | a) | <p>Design a 4 – bit Combinational shifter and briefly analyze its functioning with an appropriate truth table. Also write the stick diagram for 1 – bit inverting register.</p>                                                                                                                                                                | CO3 | PO2 | 05 |

|   | b) | <p>Implement and analyze a 4 – bit serial – parallel multiplier circuit.</p>                                                                                                                                                                                                                                                                   | CO1 | -   | 05 |

|   | c) | <p>Derive an expression for the computation time 'T' for the Carry Select Adder and thereby derive the minimum T for a 128 bit carry select adder, with 16ns delay through every adder cell and 2ns delay through the multiplexer. Determine number of blocks and number of adder cells in each block for achieving minimum T.</p>             | CO2 | PO1 | 10 |

|   |    | <b>OR</b>                                                                                                                                                                                                                                                                                                                                      |     |     |    |

| 8 | a) | <p>Design and analyze the operation of a 4 – bit Barrel shifter.</p>                                                                                                                                                                                                                                                                           | CO1 | -   | 05 |

|   | b) | <p>Implement and analyze the working of a 24 – bit Carry skip adder. Also derive the optimization technique used for the carry skip adder.</p>                                                                                                                                                                                                 | CO1 | -   | 05 |

|   | c) | <p>Consider the example of <math>(127)_{10} \times (126)_{10}</math> and thereby implement the multiplication using:</p> <ol style="list-style-type: none"> <li>Traditional Booth multiplier</li> <li>Modified Booth multiplier</li> </ol> <p>Complete the process of multiplication using appropriate encoding tables for both the cases.</p> | CO3 | PO2 | 10 |

|   |    | <b>UNIT - V</b>                                                                                                                                                                                                                                                                                                                                |     |     |    |

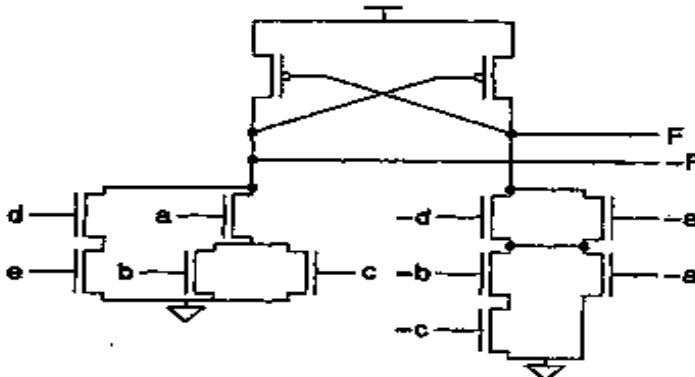

| 9 | a) | <p>Identify the memory logic in the circuit given below and thereby analyze its working principle.</p>                                                                                                                                                                                                                                         | CO2 | PO1 | 06 |

|    |    |                                                                                                                                                                                                    |     |     |           |

|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

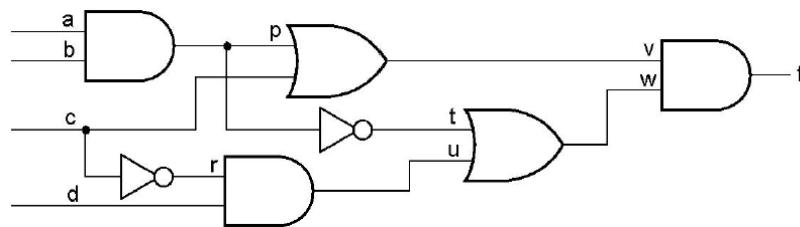

|    | b) | <p>The logic network shown below has inputs a, b, c, d and output f. Find all test vectors which can be used to find a <b>SA1</b> for signal <b>u</b>.</p>                                         | CO3 | PO3 | <b>14</b> |

|    |    | <b>OR</b>                                                                                                                                                                                          |     |     |           |

| 10 | a) | <p>Analyze the practical design issues of testability with respect to the following:</p> <ol style="list-style-type: none"> <li>Controllability and Observability</li> <li>Gated Clocks</li> </ol> | CO1 | -   | <b>06</b> |

b) The logic network shown below has inputs a, b, c, d and output f. Find all test vectors which can be used to find a **SA1** for signal **t**.

\*\*\*\*\*