|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## January / February 2025 Semester End Main Examinations

**Programme: B.E.**

**Semester: VII**

**Branch: Electronics & Telecommunication Engineering**

**Duration: 3 hrs.**

**Course Code: 22ET7PE3AD**

**Max Marks: 100**

**Course: ASIC Design**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>  |    |                                                                                                                                                                                                                              | <b>CO</b> | <b>PO</b> | <b>Marks</b> |

|------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|--------------|

| 1                | a) | Draw the flow diagram for the ASIC design and explain every step. Also, comment on logical and physical design.                                                                                                              | CO1       | PO1       | <b>10</b>    |

|                  | b) | What are the different choices of ASIC cell libraries? Discuss each of them.                                                                                                                                                 | CO1       | PO1       | <b>06</b>    |

|                  | c) | Mention the salient features of FPGA.                                                                                                                                                                                        | CO1       | PO1       | <b>04</b>    |

| <b>OR</b>        |    |                                                                                                                                                                                                                              |           |           |              |

| 2                | a) | Explain gate arrays used in semi-custom ASIC design. Discuss the different types of gates in detail with relevant figures.                                                                                                   | CO1       | PO1       | <b>12</b>    |

|                  | b) | Discuss the advantages and disadvantages of FPGA and ASIC Design in detail. When do you design circuits using full-custom design.                                                                                            | CO1       | PO1       | <b>08</b>    |

| <b>UNIT - II</b> |    |                                                                                                                                                                                                                              |           |           |              |

| 3                | a) | Describe how carry save adder reduces carry rippling, in addition. Explain how 4-input CSA is constructed using 3-input CSA. What is the need for inserting latches in the 4-input CSA?                                      | CO2       | PO1       | <b>06</b>    |

|                  | b) | Explain Wallace Tree multiplier.                                                                                                                                                                                             | CO2       | PO1       | <b>08</b>    |

|                  | c) | Draw a three-state bi-directional output buffer and explain how it works.                                                                                                                                                    | CO2       | PO1       | <b>06</b>    |

| <b>OR</b>        |    |                                                                                                                                                                                                                              |           |           |              |

| 4                | a) | Derive an expression for optimum path delay using propagation delay of the logic cascade.                                                                                                                                    | CO2       | PO2       | <b>08</b>    |

|                  | b) | For a logic path with a 1X drive minimum size inverter used to drive one input of 2X drive NOR3 logic cell in C <sub>5</sub> technology, determine the total delay. Given logic ratio r = 1.5 and C <sub>out</sub> = 0.3 pF. | CO2       | PO1       | <b>08</b>    |

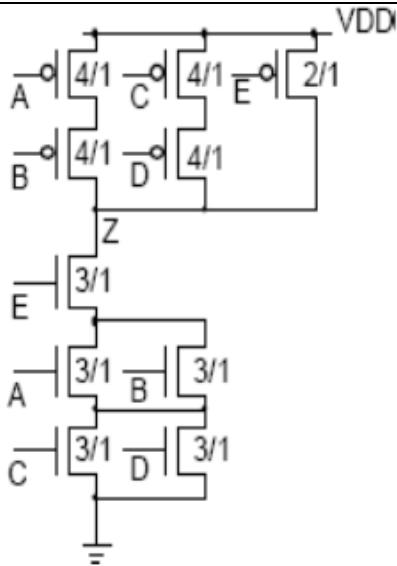

|                  | c) | For an AOI221 logic cell shown in Figure Q4(c), compute logical effort and logical area. Assume the logic ratio r = 2.                                                                                                       | CO2       | PO2       | <b>04</b>    |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

Revealing of identification, appeal to evaluator will be treated as malpractice.

**Figure Q4(c)**

**UNIT - III**

|   |    |                                                                                                                  |     |     |           |

|---|----|------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 5 | a) | With the help of a block diagram explain the XC3000 Logic Block. Also, discuss the different modes of operation. | CO3 | PO1 | <b>10</b> |

|   | b) | Develop the timing model for ACT-2 logic modules. How do you estimate the critical path between the registers?   | CO3 | PO1 | <b>10</b> |

**OR**

|   |    |                                                                                                                                                 |     |     |           |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 6 | a) | Devise the Boolean function $f = ab + b'c + d$ in the ACT1 logic module.                                                                        | CO3 | PO2 | <b>06</b> |

|   | b) | Realize the following two-input logic gates using 2:1 MUX: <ol style="list-style-type: none"> <li>NOR-11</li> <li>AND1-1</li> <li>OR</li> </ol> | CO3 | PO2 | <b>06</b> |

|   | c) | With the help of a suitable figure explain the logic element of Altera FLEX 80000 series FPGA.                                                  | CO3 | PO1 | <b>08</b> |

**UNIT - IV**

|   |    |                                                                                                           |     |     |           |

|---|----|-----------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 7 | a) | With the help of a block diagram explain Xilinx XC4000 input output block.                                | CO3 | PO1 | <b>12</b> |

|   | b) | What is supply bounce? With the help of a suitable example explain supply bounce with relevant waveforms. | CO3 | PO1 | <b>08</b> |

**OR**

|   |    |                                                                                  |     |     |           |

|---|----|----------------------------------------------------------------------------------|-----|-----|-----------|

| 8 | a) | Explain Altera's I/O control block and I/O element with suitable block diagrams. | CO3 | PO1 | <b>12</b> |

|   | b) | With suitable figure explain Xilinx LCA interconnect.                            | CO3 | PO1 | <b>08</b> |

| <b>UNIT - V</b> |    |    |                                                                                                                                              |                                 |

|-----------------|----|----|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                 | 9  | a) | What is the need for hierarchical design? Illustrate the hierarchical design for a 16-bit D latch with enable starting from primitive gates. | <i>CO3</i> <i>PO2</i> <b>12</b> |

|                 |    | b) | What is a netlist screener? Why it is used? Discuss the errors that can be found using it.                                                   | <i>CO3</i> <i>PO1</i> <b>08</b> |

| <b>OR</b>       |    |    |                                                                                                                                              |                                 |

|                 | 10 | a) | What are the difficulties of using ASIC libraries? Explain with an example.                                                                  | <i>CO3</i> <i>PO1</i> <b>06</b> |

|                 |    | b) | Justify the need for back-annotation in physical design flow.                                                                                | <i>CO3</i> <i>PO1</i> <b>06</b> |

|                 |    | c) | Illustrate the vector instances and buses for a 16-bit D latch with enable using one bit D-latch                                             | <i>CO3</i> <i>PO2</i> <b>08</b> |

\*\*\*\*\*

B.M.S.C.E. - ODD SEM 2024-25