**January / February 2025 Semester End Main Examinations**

## **Programme: B.E.**

### Semester: III

## Branch: ES CLUSTER (EC/EE/EI/ML/ET)

**Duration: 3 hrs.**

## **Course Code: 19ES3CCDEC**

**Max Marks: 100**

## Course: Digital Electronic Circuits

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>  |    |                                                                                                                                                                                                                                   |  |            |            |              |

|------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------|------------|--------------|

|                  |    |                                                                                                                                                                                                                                   |  | <b>CO</b>  | <b>PO</b>  | <b>Marks</b> |

| 1                | a) | Reduce the following circuit to minimal form                                                                                                                                                                                      |  | <i>CO1</i> | <i>PO2</i> | <b>06</b>    |

|                  | b) | Determine the simplified form for the function USING k-Map<br>$F(a, b, c, d) = \sum m(0, 2, 4, 7, 8, 10, 12)$ . Realize the simplified expression using logic gates with SOP and POS form.                                        |  | <i>CO1</i> | <i>PO2</i> | <b>14</b>    |

|                  |    | <b>OR</b>                                                                                                                                                                                                                         |  |            |            |              |

| 2                | a) | Design a logic circuit having 3 inputs, A, B, C will have its output HIGH only when a majority of the inputs are HIGH.                                                                                                            |  | <i>CO1</i> | <i>PO2</i> | <b>10</b>    |

|                  | b) | Simplify using tabulation method<br>$F(A, B, C, D) = \sum m(2, 3, 7, 9, 11, 13) + \sum d(1, 10, 15)$                                                                                                                              |  | <i>CO1</i> | <i>PO2</i> | <b>10</b>    |

| <b>UNIT - II</b> |    |                                                                                                                                                                                                                                   |  |            |            |              |

| 3                | a) | Design a 3 bit carry look ahead adder circuit.                                                                                                                                                                                    |  | <i>CO2</i> | <i>PO3</i> | <b>10</b>    |

|                  | b) | A combinational circuit is defined by the functions<br>$F_1(A, B, C) = \sum m(3, 5, 6, 7)$<br>$F_2 = (A, B, C) = \sum m(0, 2, 4, 7)$<br>Implement the circuit with a PLA having three inputs, four product terms and two outputs. |  | <i>CO2</i> | <i>PO3</i> | <b>10</b>    |

| <b>OR</b>         |    |                                                                                                                                                                                                                                                                                                                                              |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|-------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------|---|---|----------------------|---|---|------|---|---|------------|---|---|---------------|--|--|--|

| 4                 | a) | Implement the following Boolean function with a 4:1 Mux with $yz$ as select inputs $f(w, x, y, z) = \sum m(1, 3, 4, 11, 12, 14, 15)$                                                                                                                                                                                                         | <i>CO2</i> | <i>PO3</i> | <b>10</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   | b) | Consider a 4-bit adder circuit. Design a circuit that will convert the adder to a binary coded decimal form.                                                                                                                                                                                                                                 | <i>CO2</i> | <i>PO3</i> | <b>10</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| <b>UNIT - III</b> |    |                                                                                                                                                                                                                                                                                                                                              |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 5                 | a) | Draw the circuit of JK master slave flipflop and explain when the input is 10 and 11. Show the timing diagram for the same.                                                                                                                                                                                                                  | <i>CO3</i> | <i>PO3</i> | <b>08</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   | b) | Design a 4-bit ripple down counter using T flipflops.                                                                                                                                                                                                                                                                                        | <i>CO3</i> | <i>PO3</i> | <b>06</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   | c) | Design a shift register using multiplexers and D flipflops to perform the following operations.                                                                                                                                                                                                                                              | <i>CO3</i> | <i>PO3</i> | <b>06</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   |    | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr> <th>S1</th><th>S0</th><th>operation</th></tr> <tr> <td>0</td><td>0</td><td>Circular right shift</td></tr> <tr> <td>0</td><td>1</td><td>Hold</td></tr> <tr> <td>1</td><td>0</td><td>Left shift</td></tr> <tr> <td>1</td><td>1</td><td>Parallel load</td></tr> </table> | S1         | S0         | operation | 0 | 0 | Circular right shift | 0 | 1 | Hold | 1 | 0 | Left shift | 1 | 1 | Parallel load |  |  |  |

| S1                | S0 | operation                                                                                                                                                                                                                                                                                                                                    |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 0                 | 0  | Circular right shift                                                                                                                                                                                                                                                                                                                         |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 0                 | 1  | Hold                                                                                                                                                                                                                                                                                                                                         |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 1                 | 0  | Left shift                                                                                                                                                                                                                                                                                                                                   |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 1                 | 1  | Parallel load                                                                                                                                                                                                                                                                                                                                |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| <b>OR</b>         |    |                                                                                                                                                                                                                                                                                                                                              |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 6                 | a) | Convert JK to D, JK to SR flip flop                                                                                                                                                                                                                                                                                                          | <i>CO3</i> | <i>PO3</i> | <b>08</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   | b) | Design a 3-bit synchronous counter to count the sequence 0, 2, 4, 6. The unused states should reset the counter to zero. Use T flipflop                                                                                                                                                                                                      | <i>CO3</i> | <i>PO3</i> | <b>12</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| <b>UNIT - IV</b>  |    |                                                                                                                                                                                                                                                                                                                                              |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

| 7                 | a) | Define FSM. Differentiate between Mealy and Moore models.                                                                                                                                                                                                                                                                                    | <i>CO3</i> | <i>PO3</i> | <b>08</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   | b) | A sequential circuit has one input and one output. The state diagram is shown below. Design the sequential circuit with D-Flip-Flops                                                                                                                                                                                                         | <i>CO3</i> | <i>PO3</i> | <b>12</b> |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                   |    | <pre> graph LR     00((00)) -- "0/0" --&gt; 00     00 -- "1/0" --&gt; 01((01))     01 -- "0/0" --&gt; 00     01 -- "0/0" --&gt; 11((11))     11 -- "1/1" --&gt; 11     11 -- "1/0" --&gt; 10((10))     10 -- "0/1" --&gt; 10     10 -- "1/0" --&gt; 01   </pre>                                                                              |            |            |           |   |   |                      |   |   |      |   |   |            |   |   |               |  |  |  |

|                 |    | <b>OR</b>                                                                                                                                                                                                                                   |     |     |           |

|-----------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

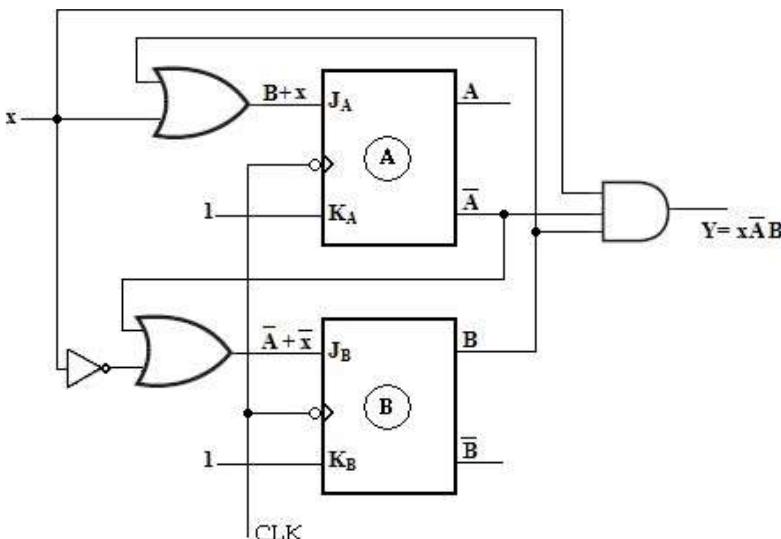

| 8               | a) | Determine the state table and state diagram for the circuit shown                                                                                                                                                                           | CO3 | PO3 | <b>10</b> |

|                 |    |                                                                                                                                                           |     |     |           |

|                 | b) | Design a Mealy state diagram to detect the sequence "101" for both overlapping and non-overlapping methods.                                                                                                                                 | CO3 | PO3 | <b>10</b> |

| <b>UNIT - V</b> |    |                                                                                                                                                                                                                                             |     |     |           |

| 9               | a) | Explain the terms<br>i) Rise time and fall time<br>ii) Propagation delay<br>iii) Noise Margin                                                                                                                                               | CO1 | PO2 | <b>08</b> |

|                 | b) | Explain the standard TTL logic circuit and explain its operation                                                                                                                                                                            | CO1 | PO2 | <b>08</b> |

|                 | c) | Draw the circuit of CMOS NOT gate                                                                                                                                                                                                           | CO1 | PO2 | <b>04</b> |

| <b>OR</b>       |    |                                                                                                                                                                                                                                             |     |     |           |

| 10              | a) | Compare TTL and CMOS ICs in terms of characteristics                                                                                                                                                                                        | CO1 | PO2 | <b>08</b> |

|                 | b) | Draw the circuit of CMOS NAND gate explain with truth table                                                                                                                                                                                 | CO1 | PO2 | <b>08</b> |

|                 | c) | A NAND gate has the following characteristics.<br><br>$I_{OH(\max)} = 2 \text{ mA}$<br>$I_{OL(\max)} = 20 \text{ mA}$<br>$I_{IH(\max)} = 20 \mu\text{A}$<br>$I_{IL(\max)} = 0.5 \text{ mA}$<br><br>Determine fanout for high and low state. | CO1 | PO2 | <b>04</b> |

\*\*\*\*\*