|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## April 2024 Semester End Main Examinations

**Programme: B.E.**

**Semester: III**

**Branch: ES Cluster (EEE/ET/EIE/MD)**

**Duration: 3 hrs.**

**Course Code: 23ES3PCDEC**

**Max Marks: 100**

**Course: Digital Electronic Circuits**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| <b>UNIT - I</b>   |    |                                                                                                                                                                                            | <b>CO</b>  | <b>PO</b>  | <b>Marks</b> |

|-------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|

| 1                 | a) | Represent the following functions in minterm and maxterms.<br>i) $F = A + BC$<br>ii) $F = XY + \bar{X}Z$                                                                                   | <i>CO1</i> | <i>PO1</i> | <b>05</b>    |

|                   | b) | Find the prime implicants and essential prime implicants for the following function using K-map technique<br>$f(A, B, C, D) = \sum m(0, 2, 5, 7, 8, 10, 13, 15) + \text{dc}(1, 4, 11, 14)$ | <i>CO1</i> | <i>PO1</i> | <b>07</b>    |

|                   | c) | Simplify the following Boolean function by using Quine-McClusky method and determine the prime implicants<br>$F(A, B, C, D) = \sum (1, 4, 6, 7, 8, 9, 10, 11, 15)$                         | <i>CO1</i> | <i>PO1</i> | <b>08</b>    |

| <b>UNIT - II</b>  |    |                                                                                                                                                                                            |            |            |              |

| 2                 | a) | Implement the given Boolean function using 4 : 1 multiplexer<br>$F(A, B, C) = \sum (0, 4, 5, 6)$                                                                                           | <i>CO2</i> | <i>PO2</i> | <b>04</b>    |

|                   | b) | Implement the following two Boolean functions with a PLA:<br>$F1(A, B, C) = \sum(0, 1, 2, 4)$ and $F2(A, B, C) = \sum(0, 5, 6, 7)$                                                         | <i>CO2</i> | <i>PO2</i> | <b>08</b>    |

|                   | c) | Explain carry look ahead generation with the help of logic diagram (4-bit).                                                                                                                | <i>CO2</i> | <i>PO2</i> | <b>08</b>    |

| <b>OR</b>         |    |                                                                                                                                                                                            |            |            |              |

| 3                 | a) | Design a 2-bit magnitude comparator to compare two 2 bit number with logic diagram.                                                                                                        | <i>CO2</i> | <i>PO2</i> | <b>10</b>    |

|                   | b) | Implement the following Boolean pairs using a decoder with minimum input gates<br>$F1(a, b, c) = \pi M(1, 2, 4, 6)$<br>$F2(a, b, c) = \pi M(2, 4, 7)$                                      | <i>CO2</i> | <i>PO2</i> | <b>04</b>    |

|                   | c) | Design a 3-bit binary to gray code converter using a ROM.                                                                                                                                  | <i>CO2</i> | <i>PO2</i> | <b>06</b>    |

| <b>UNIT - III</b> |    |                                                                                                                                                                                            |            |            |              |

| 4                 | a) | What is race around condition in flip flops? Explain how it can overcome?                                                                                                                  | <i>CO2</i> | <i>PO2</i> | <b>06</b>    |

|                   | b) | Convert JK flip flop to D flip flop.                                                                                                                                                       | <i>CO3</i> | <i>PO3</i> | <b>06</b>    |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. Revealing of identification, appeal to evaluator will be treated as malpractice.

|   |    |                                                                                                                                                                                                                                                  |     |     |           |

|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|   | c) | Design a synchronous Mod-6 (count sequence 0, 1, 2, 3, 4, 5) counter using clocked D flip-flops.                                                                                                                                                 | CO2 | PO2 | <b>08</b> |

|   |    | <b>OR</b>                                                                                                                                                                                                                                        |     |     |           |

| 5 | a) | Explain the working of a Master-slave JK flip flop with functional table and timing diagram.                                                                                                                                                     | CO2 | PO2 | <b>08</b> |

|   | b) | Design a 4-bit ripple up counter using negative edge triggered JK flip flops                                                                                                                                                                     | CO3 | PO3 | <b>05</b> |

|   | c) | Convert with the help of function table and excitation table JK flip flop to SR flip flop.                                                                                                                                                       | CO2 | PO2 | <b>07</b> |

|   |    | <b>UNIT - IV</b>                                                                                                                                                                                                                                 |     |     |           |

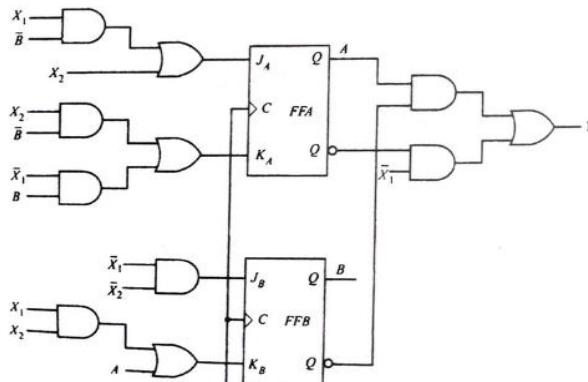

| 6 | a) | Construct the excitation table, transition table, state table and state diagram for the synchronous sequential circuit shown in Figure 6.a                                                                                                       | CO3 | PO3 | <b>12</b> |

|   |    |                                                                                                                                                               |     |     |           |

|   |    | Figure 6.a                                                                                                                                                                                                                                       |     |     |           |

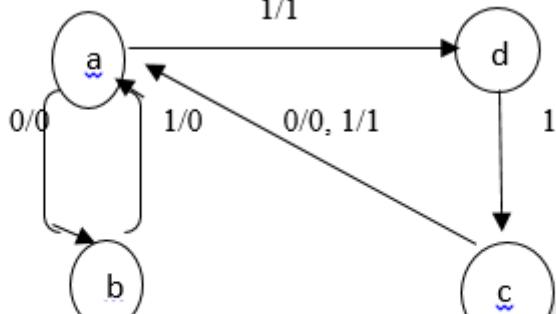

|   | b) |  <p><u>State Assignment</u> <u>a:00</u> <u>b:01</u>, <u>c:10</u>, <u>d:11</u></p> <p>Design a sequential circuit for the above state diagram using T-FFs</p> | CO3 | PO3 | <b>08</b> |

|   |    | <b>UNIT - V</b>                                                                                                                                                                                                                                  |     |     |           |

| 7 | a) | Design a CMOS inverter and explain its operation. Compare its characteristics over TTL logic families such as Fan - in, Fan - out, power dissipation, propagation delay, switching speed and noise margin.                                       | CO1 | PO1 | <b>14</b> |

|   | b) | With circuit schematic explain the working of a two - input TTL NAND gate.                                                                                                                                                                       | CO1 | PO1 | <b>06</b> |

\*\*\*\*\*