|        |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

| U.S.N. |  |  |  |  |  |  |  |  |

|--------|--|--|--|--|--|--|--|--|

# B.M.S. College of Engineering, Bengaluru-560019

Autonomous Institute Affiliated to VTU

## July 2024 Semester End Main Examinations

**Programme: B.E.**

**Branch: Medical Electronics Engineering**

**Course Code: 22MD5PE1VL**

**Course: VLSI DESIGN**

**Semester: V**

**Duration: 3 hrs.**

**Max Marks: 100**

**Instructions:** 1. Answer any FIVE full questions, choosing one full question from each unit.

2. Missing data, if any, may be suitably assumed.

| UNIT - I                                                                                           |    |                                                                                                                                                                                                                                                                                                                              | CO  | PO  | Marks     |

|----------------------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 1                                                                                                  | a) | Design a CMOS logic gate for the function<br>$F = \text{not} (a.b + a.c + b.d)$ using minimal transistor count.                                                                                                                                                                                                              | CO1 | PO1 | <b>06</b> |

|                                                                                                    | b) | Design a 4:1 MUX using three 2:1 TG multiplexors.                                                                                                                                                                                                                                                                            | CO1 | PO1 | <b>06</b> |

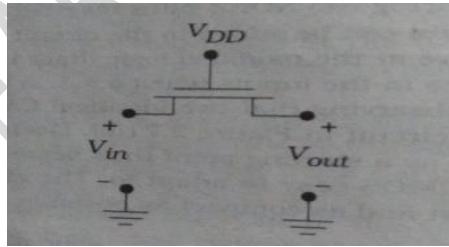

|                                                                                                    | c) | Suppose that $V_{DD} = 5$ V and $V_{Th} = 0.7$ V. Find the output voltage $V_{out}$ of the nFET in Figure 1.c for the following input voltage values:<br>i) $V_{in} = 2$ V<br>ii) $V_{in} = 4.5$ V<br>iii) $V_{in} = 3.5$ V<br>iv) $V_{in} = 0.7$ V                                                                          | CO1 | PO1 | <b>08</b> |

| <br>Figure 1.c |    |                                                                                                                                                                                                                                                                                                                              |     |     |           |

| <b>OR</b>                                                                                          |    |                                                                                                                                                                                                                                                                                                                              |     |     |           |

| 2                                                                                                  | a) | With a neat diagram explain the CMOS NOR2 gate functionality.                                                                                                                                                                                                                                                                | CO1 | PO1 | <b>06</b> |

|                                                                                                    | b) | Design a TG-based 2-to-1 multiplexor and explain its working                                                                                                                                                                                                                                                                 | CO1 | PO1 | <b>06</b> |

|                                                                                                    | c) | Consider the 2-input XOR function a XOR b.<br>i) Design an XOR gate using a 4:1 MUX.<br>ii) Modify the circuit in (i) to produce a 2-input XNOR.<br>iii) A full adder accepts inputs a, b and c and calculates the sum bit $s = a \text{ XOR } b \text{ XOR } c$ . Use MUX-based gates to design a circuit with this output. | CO1 | PO1 | <b>08</b> |

| <b>UNIT - II</b>                                                                                   |    |                                                                                                                                                                                                                                                                                                                              |     |     |           |

| 3                                                                                                  | a) | Consider the logic function $F = \text{not}(a+b.c)$                                                                                                                                                                                                                                                                          | CO2 | PO3 | <b>08</b> |

**Important Note:** Completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

Revealing of identification, appeal to evaluator will be treated as malpractice.

|                   |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |           |

|-------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

|                   |    | Design the CMOS logic gate and layout that provides this function.                                                                                                                                                                                                                                                                                                                                                      |     |     |           |

|                   | b) | An interconnect line runs over an insulating oxide layer that is 10,000 Å thick. The line has a width of 0.5 $\mu\text{m}$ and is 40 $\mu\text{m}$ long. The sheet resistance is known to be $25\Omega$ .<br>i) Find the line resistance.<br>ii) Find the line capacitance. Use $\epsilon_{\text{ox}}=3.453 \times 10^{13} \text{ F/cm}^2$ , and express your answer in femto farads where $1\text{fF}=10/15\text{F}$ . | CO2 | PO3 | <b>06</b> |

|                   | c) | Construct the Euler's graph for the function $g = \text{not } (a+b.c)$ .                                                                                                                                                                                                                                                                                                                                                | CO2 | PO3 | <b>06</b> |

| <b>UNIT - III</b> |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |           |

| 4                 | a) | With neat sketches explain the voltage transfer curve for the NOT gate.                                                                                                                                                                                                                                                                                                                                                 | CO3 | PO2 | <b>06</b> |

|                   | b) | With neat diagram explain the NAND2 VTC analysis along with the transition table.                                                                                                                                                                                                                                                                                                                                       | CO3 | PO2 | <b>07</b> |

|                   | c) | With proper analysis prove $k'n/k'p = \mu_n/\mu_p = r$ .                                                                                                                                                                                                                                                                                                                                                                | CO3 | PO2 | <b>07</b> |

| <b>UNIT - IV</b>  |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |           |

| 5                 | a) | With a neat sketch derive the sheet resistance equation and give two reasons about its importance.                                                                                                                                                                                                                                                                                                                      | CO3 | PO2 | <b>07</b> |

|                   | b) | With simple analysis estimate the rise-time for a CMOS inverter.                                                                                                                                                                                                                                                                                                                                                        | CO3 | PO2 | <b>07</b> |

|                   | c) | Discuss the ways to route data and control signals for choice between the layers.                                                                                                                                                                                                                                                                                                                                       | CO3 | PO2 | <b>06</b> |

| <b>OR</b>         |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |           |

| 6                 | a) | With simple analysis estimate the fall-time for a CMOS inverter.                                                                                                                                                                                                                                                                                                                                                        | CO3 | PO2 | <b>07</b> |

|                   | b) | Calculate the delay for driving large capacitive loads.                                                                                                                                                                                                                                                                                                                                                                 | CO3 | PO2 | <b>07</b> |

|                   | c) | Discuss on the design of long polysilicon wires.                                                                                                                                                                                                                                                                                                                                                                        | CO3 | PO2 | <b>06</b> |

| <b>UNIT - V</b>   |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |           |

| 7                 | a) | Calculate the effects of scaling for gate area, gate capacitance, parasitic capacitance, channel resistance and gate delay.                                                                                                                                                                                                                                                                                             | CO4 | PO4 | <b>10</b> |

|                   | b) | Discuss the limitations of scaling (Any two).                                                                                                                                                                                                                                                                                                                                                                           | CO4 | PO4 | <b>05</b> |

|                   | c) | Analyze the guidelines to be followed for large system designs in MOS technology.                                                                                                                                                                                                                                                                                                                                       | CO4 | PO4 | <b>05</b> |

\*\*\*\*\*